【开发者分享】 利用 RQA 和 RQS 实现设计收敛

judy 在 周五, 07/31/2020 - 10:37 提交

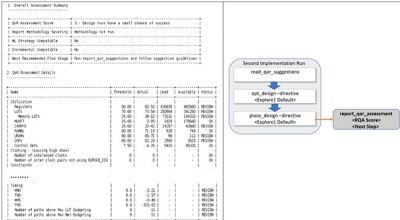

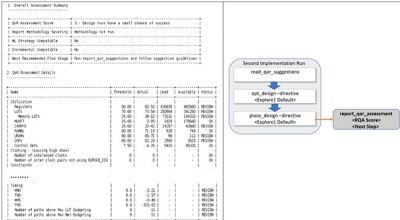

通过之前的博文,我们已经学会了如何使用 Report QoR Assessment (RQA) 和 Report QoR Suggestions (RQS) 来改进总体设计分析以及设计的时序收敛体验。本篇博文将通过一个具体设计示例来演示如何在实现流程中将 RQA 与 RQS 结合使用。

通过之前的博文,我们已经学会了如何使用 Report QoR Assessment (RQA) 和 Report QoR Suggestions (RQS) 来改进总体设计分析以及设计的时序收敛体验。本篇博文将通过一个具体设计示例来演示如何在实现流程中将 RQA 与 RQS 结合使用。

首届赛灵思自适应计算挑战赛(Xilinx Adaptive Computing Challenge)继续火热报名中!为了帮助国内开发者更好更快地报名成功,Xilinx技术社区帮您简化流程,手把手教您如何报名开发者比赛,赢万元大奖!

很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及LVDS-33,LVDS-25)信号相连时兼容性的问题,该专题就解决一下这类问题。

随着新一代网络被部署用来支持日益多样化的高带宽应用组合,网络供应商和数据中心运营商需要快速扩展数据包处理能力,同时最大限度地降低资本支出/运营成本,并保持灵活性,从而适应未来的连接标准。为满足未来的不同需求,赛灵思推出了Kintex UltraScale+ KU19P FPGA。

随着在数据驻留位置附近对数据进行处理的性能优势得到充分体现,计算存储持续受到广泛关注。行业的发展势头正在形成,存储网络工业协会 (SNIA) 等组织正在通过计算、存储器和存计划帮助定义计算存储的方式、内容、位置和原因。SNIA 帮助确定的计算存储类型之一是计算存储处理器 (CSP)

随着 AI 模型所需算力发生数量级增长, AI 推断对于硬件的需求大大增加。而摩尔定律的日渐式微,让架构创新成为希望之星。只有特定领域架构(DSA)才能确保硬件可以跟上不断增长的 AI 推断需求——DSA代表着未来计算,即为“每种类型的工作负载”定制自适应硬件,以实现最高的运行效率

赛灵思今日宣布加入 Open RAN 政策联盟,致力于为Open RAN 5G 技术的开发和部署提供有力支持。Open RAN 政策联盟的成员提倡将 Open RAN 作为首选解决方案,提高多厂商生态系统的互操作性和安全性。

Aupera Aup2600 系列提供了面向视频处理的模块化和分布式计算架构,打破了基于 x86 处理器的传统解决方案的瓶颈。

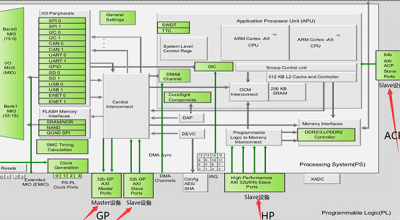

如果说要在AXI、AXI-Lite、AXI-Stream中选一种最喜欢的类型,我选择Stream总线,因为这是最简单的类型,而且使用起来非常方便,五个通道就剩数据传输,就像网络通信中的TCP与UDP,UDP用起来更简洁。

AXI(Advanced extensible Interface)协议主要描述了Master设备和Slave设备之间的数据传输方式,Master设备和Slave设备之间通过握手信号建立连接。当Slave设备的数据准备好时,会发出和维持VALID信号,表示数据有效;当Master设备准备好接收数据时,会发出READY信号。数据只有在这两个信号都有效时才开始传输。