Xilinx 和 Aupera - 实时视频分析解决方案

judy 在 周三, 07/29/2020 - 16:04 提交

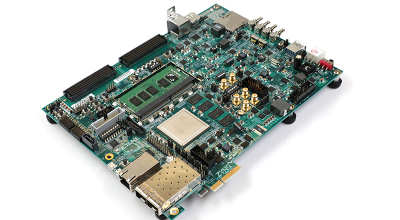

Aupera Aup2600 系列提供了面向视频处理的模块化和分布式计算架构,打破了基于 x86 处理器的传统解决方案的瓶颈。

Aupera Aup2600 系列提供了面向视频处理的模块化和分布式计算架构,打破了基于 x86 处理器的传统解决方案的瓶颈。

如果说要在AXI、AXI-Lite、AXI-Stream中选一种最喜欢的类型,我选择Stream总线,因为这是最简单的类型,而且使用起来非常方便,五个通道就剩数据传输,就像网络通信中的TCP与UDP,UDP用起来更简洁。

AXI(Advanced extensible Interface)协议主要描述了Master设备和Slave设备之间的数据传输方式,Master设备和Slave设备之间通过握手信号建立连接。当Slave设备的数据准备好时,会发出和维持VALID信号,表示数据有效;当Master设备准备好接收数据时,会发出READY信号。数据只有在这两个信号都有效时才开始传输。

高层次综合(High-level Synthesis)简称 HLS,指的是使用C、C++、System C 等高层次语言描述电路设计的逻辑结构,以及编写对应的测试激励,借助高层次综合工具,配合高阶约束文件及优化指令自动转换成低抽象级语言(VHDL/Verilog)描述的电路模型的过程。

本次系列研讨会将由赛灵思战略应用高级工程师 Lauren Gao(高亚军)带领大家从基础到进阶,一站式领略 Vivado 这款神奇的开发工具。

米尔科技的FZ3是与百度紧密合作推出的一款基于Xilinx Zynq Ultrascale CZU3EG芯片打造的深度学习计算卡,芯片内部集成了4核ARM A53处理器+GPU+FPGA的架构,具有多核心处理能力、FPGA可编程能能力以及视频流硬件解码能力等特点。

本章将着重讲述PCIe物理层组成与操作,物理层位于数据链路层之下,可产生PLP包(Physical Layer Packet)进行管理。

250-M2D 采用了完全可编程的赛灵思® Kintex® UltraScale+™ FPGA,直接耦合到本地 DDR4 内存的两个存储器组上。可以完全由客户进行完全自主编程,或者采用Eideticom 的应用 IP,作为可立即运行的预编程解决方案来交付,后者是快速发展的计算存储市场上广受认可的领导者

Enyx 开发框架 (nxFramework) 是一个软硬件开发环境,旨在为金融行业高效构建和维护超低时延的 FPGA 应用。nxFramework 建立在 10 年的研发基础之上,是所有 Enyx 现成解决方案的基础,可为客户提供管理一系列大量应用的工具链。

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。在ZCU106单板上,有312个Block RAM,有96个Ultra RAM。客户需要1MB存储空间。