【视频】Zynq UltraScale + RFSoC 设计方法

judy 在 周三, 07/15/2020 - 15:08 提交

2019 XDF 演示文稿:RFSoC 工具和多频带支持示例

2019 XDF 演示文稿:RFSoC 工具和多频带支持示例

在上篇文章中了整理了一些针对开发者参加本次挑战赛的常见问题并解答,本期文章将对初创企业参赛的一些常见问题整理并解答。

这大半年一直在做一个高速板卡FPGA相关的方方面面的工作,包括前期FPGA架构布局设计,管脚验证,后期实现资源优化,最后到板卡调试。过程曲折艰辛,但是也收获良多。今天在这里记录下工作中零零散散的记录下来。

本次系列研讨会将由赛灵思战略应用高级工程师 Lauren Gao(高亚军)带领大家从基础到进阶,一站式领略 Vivado 这款神奇的开发工具。

赛灵思人工智能高级总监姚颂为大家详解AI芯片技术与产业发展路径

Megh 开发了视频分析解决方案 (VAS) 来解决零售供应链中的库存损耗问题。该解决方案主要针对不同的使用案例,包括零售场所的防欺诈、制造中的库存跟踪,以及物理安全的视频监控等。 该解决方案在 Megh 的实时分析平台上运行,该平台可将整个实时分析流水线映射到集成在用户应用中的多个联网 FPGA 中

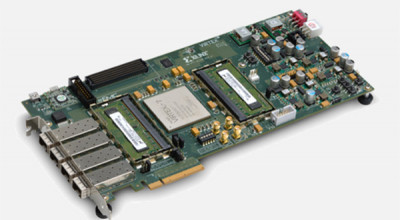

Zynq® UltraScale+™ RFSoC ZCU208 评估套件是面向开箱即用评估及前沿应用开发的理想 RF 测试平台。该套件包含 UltraScale+ RFSoC ZU48DR,其集成 8 个 14 位 5GSPS ADC、8 个 14 位 10GSPS DAC 以及 8 个软决策前向纠错 (SD-FEC) 内核,专为快速启动 RF 类应用而设计

此次“自适应计算挑战赛”面向所有独立开发者和初创企业。比赛要求使用 Vitis / Vitis AI 在 Xilinx 平台上实现算法和应用的硬件加速。获奖者将获得奖金! 立即注册并开始设计吧!

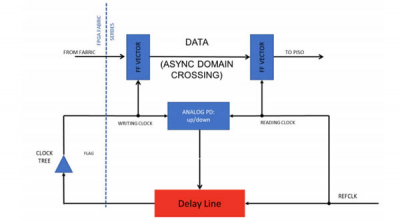

在Xilinx平台上,可实现的PTP精度受所用架构而不是硬件的限制。这是一种范式转换,它使开发人员可以在仍使用标准硬件平台的情况下达到其应用程序所寻找的精度。

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实