FPGA的软核、硬核、固核

judy 在 周一, 07/06/2020 - 10:05 提交

现在的FPGA设计,规模巨大而且功能复杂,因此设计的每一个部分都从头开始是不切实际的。一种解决的办法是:对于较为通用的部分可以重用现有的功能模块,而把主要的时间和资源用在设计中的那些全新的、独特的部分。这就像是你在开发应用程序的时候就不用直接去写驱动物理硬件的代码

现在的FPGA设计,规模巨大而且功能复杂,因此设计的每一个部分都从头开始是不切实际的。一种解决的办法是:对于较为通用的部分可以重用现有的功能模块,而把主要的时间和资源用在设计中的那些全新的、独特的部分。这就像是你在开发应用程序的时候就不用直接去写驱动物理硬件的代码

EasyDL是百度大脑推出的定制化AI训练及服务平台,支持面向各行各业有定制AI需求的企业用户及开发者使用。支持从数据管理与数据标注、模型训练、模型部署一站式AI开发流程,通过原始图片、文本、音频、视频类数据经过EasyDL加工、学习、部署可发布为公有云API、设备端SDK、本地化部署及软硬一体产品

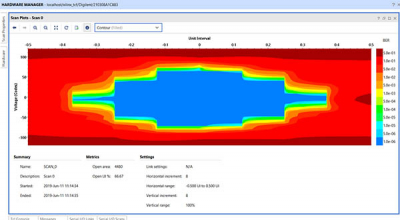

In-system IBERT 可提供 PCIe 链接眼图。“JTAG Debugger”和“In-system IBERT”功能结合在一起即可提供即时信息,用于判断链接训练问题的可能原因。在本篇博文中,我们将讲解如何使用这些功能。本篇博文基于赛灵思 VCU118 开发板随附的 UltraScale+ 器件。

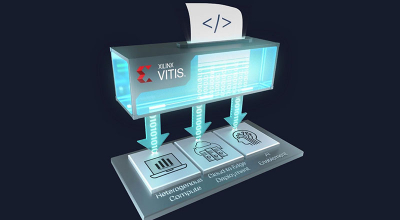

Vitis™统一软件平台是一种新的工具,它将Xilinx®软件开发的所有方面结合到一个统一的环境中。适合从边缘到云的所有开发者。Vitis 统一软件平台 2020.1 现已推出下载

赛灵思宣布 Virtex UltraScale+ 系列产品再添独一无二的高速运算新成员 — Virtex UltraScale+ VU57P FPGA。这是一款新型高带宽内存(HBM)组件,能够在极快速度、低延迟和极低功耗需求下传输大量数据。新型 Virtex UltraScale+ VU57P FPGA 融合了一系列强大的功能,适用于数据中心及有线与无线通信中要求最严苛的众多应用

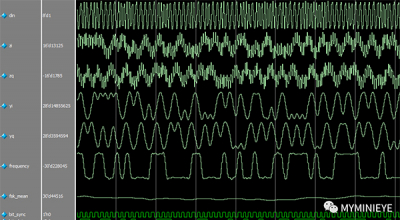

FSK信号的解调也有非相干和相干两种,FSK信号可以看作是用两个频率源交替传输得到的,所以FSK的接收机由两个并联的ASK接收机组成。

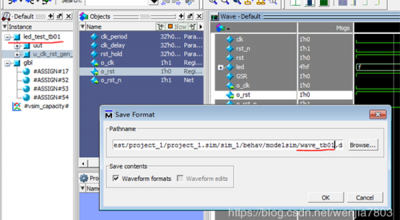

之前有分享过《modelsim se 2019.2安装教程》及《vivado2018 中使用modelsim联合仿真》,今天就带来Vivado与Modesim联合仿真的一些注意点

基于新型的赛灵思实时服务器( Xilinx RT Server)参考架构,两大全新一体机将双管齐下,助力当今服务提供商以每通道最低成本提供视频质量和比特率优化的多种类型应用。本文我们将开始为您揭开这一与众不同的实时转码一体机...

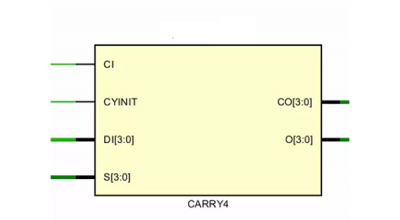

在FPGA中我们写的最多的逻辑是什么?相信对大部分朋友来说应该都是计数器,从最初板卡的测试时我们会闪烁LED,到复杂的AXI总线中产生地址或者last等信号,都会用到计数器,使用计数器那必然会用到进位链。

如果您正在使用 MATLAB 建模数字信号处理(DSP)或者视频和图像处理算法,并且最终将其用于 FPGA 或 ASIC,本文可能将为你带来帮助。