构建更理想的原型验证平台

judy 在 周一, 06/22/2020 - 09:44 提交

当我们打算进行ASIC或是SoC原型验证的时候, FPGA或许是我们最好的选择。各大厂商正努力提升工艺水平,制造拥有更高逻辑密度和更大I/O 数量的FPGA。Xilinx 未来将要上市的VU19P拥有 900 万个系统逻辑单元,为搭建当今最复杂 SoC与ASIC的原型与提供了条件。

当我们打算进行ASIC或是SoC原型验证的时候, FPGA或许是我们最好的选择。各大厂商正努力提升工艺水平,制造拥有更高逻辑密度和更大I/O 数量的FPGA。Xilinx 未来将要上市的VU19P拥有 900 万个系统逻辑单元,为搭建当今最复杂 SoC与ASIC的原型与提供了条件。

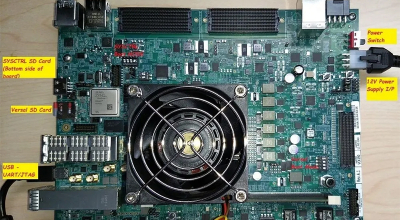

Versal™ ACAP(自适应计算加速平台)是高度集成化的多核计算平台,可通过灵活的自适应能力来满足不断变化的动态算法的需求。VCK190 是赛灵思最早发布的 Versal AI Core 评估器件之一。本篇博文将为您详解如下所述设计创建步骤:

本文介绍MPSoC的芯片启动流程

本白皮书探讨如何将 Xilinx® Vivado® HLS 环境中开发的现有 HLS 设计移植到 Mentor 的 Catapult® HLS 平台中。

了解嵌入式软件(如 Linux、Xen Hypervisor 和免费实时操作系统)与构建工具(如 Yocto 和 PetaLinux)在 2020.1 发布周期中的新特性。 该视频将详细介绍在该发布周期中所有的新增功能与修改内容

无论您是使用 Xilinx 产品进行应用设计的专家还是初学者,都可通过参加我们的培训,轻松掌握设计技巧与方法。 激发创造力,进一步提升自适应计算系统开发的设计技能。

结合 SDSoC 和赛灵思 SDK,SDAccel 流现在是 2019.2 Vitis™ 统一软件平台的组成部分,便于开发者针对赛灵思器件上的所有软件任务使用统一平台。下面分享来自 DesignLinx 公司高级嵌入式软件工程师 Nathan Sullivan 所撰写的技巧

本期导读

在 AI 领域,图像理解是一个重要分支,而图像语义分割,是计算机视觉技术中关于图像理解的重要环节。《用于语义分割的双重超分辨率学习》这篇论文针对的就是计算机视觉中的语义分割算法进行的创新研究。此次研究中的工作主要集中在语义分割领域,我们希望通过提出新的算法思路,促进语义分割领域的研究发展,启发语义分割乃至其他领域的后续研究。

Vivado® Design Suite HLx 版本可为设计团队提供实现基于 C 的设计、重用优化、IP 子系统重复、集成自动化以及设计收敛加速所需的工具和方法。与 UltraFast™ 高层次生产力设计方法指南相结合,这种特殊组合经过验证,不仅可帮助设计人员以高层次抽象形式开展工作,同时还可促进重复使用,从而可加速生产力

Vivado 2020.1 新增以下功能:

能够将完整的图像或选定的产品作为 Web 安装程序的一部分

增强的地址映射,用于实时错误高亮显示和交叉探测

Report QoR Suggestions 功能可预测多达 3 种自定义策略,以提升性能

嵌套 DFX 为您的 DFX 解决方案提供了更大的灵活性

基于电源通道的报告