是否采用 Versal?这是个问题……

judy 在 周三, 08/26/2020 - 15:00 提交

在我与客户交流时,常被问到这个问题。也许措辞并非完全如此,但大致是下面这样:“为什么我要升级到 Versal™ ACAP?现在是时候这样做了吗?”这是一个很好的问题,而且答案也很简单,那就是——“具体情况具体分析”。

在我与客户交流时,常被问到这个问题。也许措辞并非完全如此,但大致是下面这样:“为什么我要升级到 Versal™ ACAP?现在是时候这样做了吗?”这是一个很好的问题,而且答案也很简单,那就是——“具体情况具体分析”。

在 5G 商业化方兴未艾之际,对于 5G 能给我们这个日益互联的世界带来哪些影响,人们充满憧憬。事实上,随着 5G 技术得到更广泛的部署,今后十年我们预计将看到消费者、企业和经济的面貌被 5G 功能重塑一新。

赛灵思自适应挑战赛个人赛福利已经接近尾声,为了让已参赛者和跃跃欲试者能发挥出更好的比赛水平,我们特面向参赛选手录制了针对三个不同项目的赛前指导与培训。(小编悄悄地说,没有报名的人也可以收看哈,说不定看完之后您也就想参赛了,毕竟,这不还有15个免费 Ultra96-V2 的免费福利嘛~~)

一站式赛灵思工业、视觉与医疗资源库建设完成,我们将涉及工业、视觉与医疗应用领域的相关技术文档、视频资源汇集整理奉献给广大同行业者

在 2019.1 版本中,在以下情况下,当数据小于 104 字节时,XilSecure 不支持 SHA3 散列计算:

输入数据处于非字对齐状态

输入数据来自非字对齐地址。

该视频演示了使用基于 Xilinx FPGA 的网络加速卡在虚拟基站中进行 CU 处理的优势。

本应用说明介绍了选择串行外设接口(SPI)闪存作为Xilinx 7系列FPGA的配置存储器存储的优势以及实现该解决方案的细节。

Grovf 现在提供其卸载引擎 Hyperon,它是一组在 FPGA 芯片上实现的基本编程算法,与简单易用的主机驱动程序集成。Hyperon 提供算法的加速版本,例如:正则表达式(RegEx,几乎完全支持)、文本相似性匹配、搜索、排序、线性代数(矩阵转置、点积、范数平方、矩阵相乘)以及无损数据压缩等

在此演示视频中,我们将介绍 O-RAN gNB-DU L1 硬件加速和前传卸载。

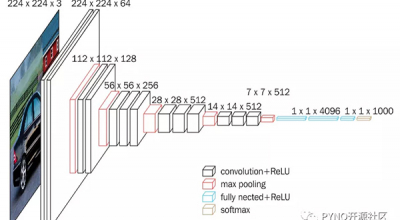

上期推送为大家带来了A班的优秀作品合集。本期,小编为大家带来了B班优秀作品的基于PYNQ的SSD目标检测系统项目。B班的作品相较于A班更有挑战性,内容也更丰富一些。本篇推送主要介绍设计概述,如果有想要亲自尝试本系统的同学,请复制下方Github链接前往GitHub,即可看到本项目的开源代码哦!