【视频】斯巴鲁选择 Xilinx 助力新一代 EyeSight 系统

judy 在 周五, 09/04/2020 - 13:28 提交

Xilinx Zynq® UltraScale+™ MPSoC 技术助力斯巴鲁基于视觉的高级驾驶辅助系统(ADAS)新一代 EyeSight。集成在全新斯巴鲁 Levorg 车型的新版 EyeSight 系统,将为其提供包括自适应巡航控制、行车道保持辅助和预碰撞制动等先进特性,将一流的安全技术交付至消费者手中。

Xilinx Zynq® UltraScale+™ MPSoC 技术助力斯巴鲁基于视觉的高级驾驶辅助系统(ADAS)新一代 EyeSight。集成在全新斯巴鲁 Levorg 车型的新版 EyeSight 系统,将为其提供包括自适应巡航控制、行车道保持辅助和预碰撞制动等先进特性,将一流的安全技术交付至消费者手中。

这篇博客主要记录Vivado中除法IP的注意事项,遇见一些新的知识点应该做相应的笔记。

Rapanda 提供了在 FPGA 上运行的内联端到端流管道。Rapanda 为即将到来的 Event Tsunami 提供大数据流处理和机器学习的加速。

由于高能粒子的撞击,器件的存储单元内容有可能受到干扰,甚至出现翻转。这种单个存储单元的翻转现象(原有内容为0的变成1;或者原有为1的变成了0)就称为SEU (Single Event Upset)。下面我们就基于KCU116开发板,介绍一下如何在设计中加入一个最基本功能的SEM IP,从而开启芯片的SEU检测功能。

作为业界公认的人工智能风向标,Gartner每年发布的AI技术成熟度曲线一直备受关注。该曲线可以为CIO、AI领导者以及数据和分析领导者提供AI新兴技术蓝图及行动参考。近日,Gartner 2020AI技术成熟度曲线出炉,并提出AI领域两大主导趋势

本期小编继续为大家带来暑期学校优秀作品分享之加密算法相关项目!对计算机安全或者密码学感兴趣的同学千万不要错过哟!

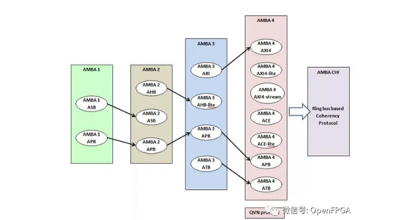

在基于IP复用的SoC设计中,片上总线设计是最关键的问题。为此,业界出现了很多片上总线标准。其中,由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。

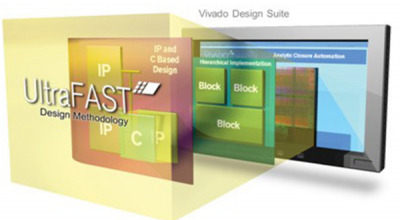

在本文中,我们将讲解如何在 Vivado® Design Suite 中完成平台准备工作,以便将其用作为 Vitis 中的加速平台。

本文描述了用于实现赛灵思 FPGA 器件资源的有效利用以及在 Vivado® Design Suite 中加速设计实现和时序收敛的推荐设计方法论。提供推荐方法背后的原理,以支持用户制定出明智的设计决策。

8月27日,我们与风河公司共同举办的“软件定义汽车(SDV):实时操作系统赋能自动驾驶”研讨会受到了大家的广泛关注。会上有观众提出了许多极具建设性的问题,小编在这里贴心地为大家总结了会上的提问,并给予了专业答复