强强联合,解决“小黄人”难题!Xilinx 携手 Nimbix 与三星提速云应用

judy 在 周二, 03/31/2020 - 09:20 提交

我们不妨将并行计算单元想象成一个塞满小黄人的小型棒球场,每个小黄人代表 100 万个逻辑门。一旦某个任务不支持所有小黄人同时并行工作,GPU 这样的并行计算加速器就会面临严重的性能瓶颈。

我们不妨将并行计算单元想象成一个塞满小黄人的小型棒球场,每个小黄人代表 100 万个逻辑门。一旦某个任务不支持所有小黄人同时并行工作,GPU 这样的并行计算加速器就会面临严重的性能瓶颈。

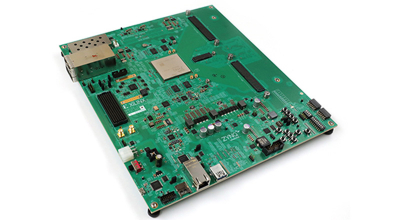

Zynq® UltraScale+™ RFSoC ZCU216 评估套件配备业界唯一单芯片自适应射频平台,是快速原型设计和高性能 RF 应用开发的理想平台。ZCU216 评估套件配备 Zynq UltraScale+ RFSoC Gen 3 ZU49DR,可采用 16T16R 高速 RF-DAC 及 RF-ADC 实现 6GHz 以下频段的直接 RF 采样。

通过视频简要了解整个 Xilinx 嵌入式处理产品组合中 Xilinx嵌入式软件堆栈中的组件。

继续学习ZYNQ,吃了好几年灰的ZYNQ 7020开发板一直没时间玩,现在稍微有点时间,准备空闲之余折腾一下,之前一直使用STM32等各式单片机,LINUX知识也知道一点,对HDL也是一窍不通,现在准备恶补一下,对于我来说,学习固然重要,但是白费力折腾也是要有的

本文内容来自Xilinx 张吉帅在LiveVideoStackCon2019深圳站上的精彩分享,他将重点讨论异构计算中非常具有潜力的一部分 —— FPGA,并详细介绍赛灵思以及其技术生态合作伙伴在有关视频加速,图片转码等方面的解决方案。

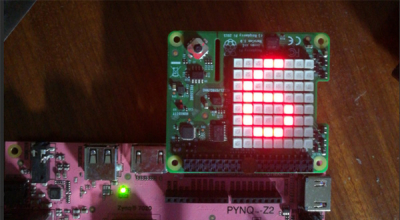

本项目介绍了Sense HAT在PYNQ上的使用。Sense HAT是是为树莓派设计的集成外设板,包含了惯性传感器、湿度温度传感器、气压传感器和一个8×8LED矩阵。这些外设通过I2C总线利用不同设备地址来访问。本项目分成三个部分介绍:LED矩阵显示字符、温度气压传感器读取和惯性传感器数据读取

或许是每个做硬件的厂商都有做软件的心,xilinx发布了他的下一个平台Vitis,也就是硬件和软件分开了(即Vivado和IDE分开了),除了启动方式和使用方法略有区别外,其他操作几乎与上一代Vivado一模一样。本文是试用这个新平台来尝尝鲜。

赛灵思 AXI Verification IP (AXI VIP) 是支持用户对 AXI4 和 AXI4-Lite 进行仿真的 IP。它还可作为 AXI Protocol Checker 来使用。此 IP 只是仿真 IP,将不进行综合(它将在 Pass-through 配置中被连线所替代)。

“灵活应变”是赛灵思经常使用的一个词语。今天,这个词语显得比以往任何时候都更有意义。整个赛灵思大家庭 – 包括我们的员工,我们尊敬的客户,还有我们的合作伙伴们,在这样一个全球COVID-19(新冠状肺炎病毒)疫情蔓延的艰难时期,定义了真正的“自适应能力”和“灵活应变能力”

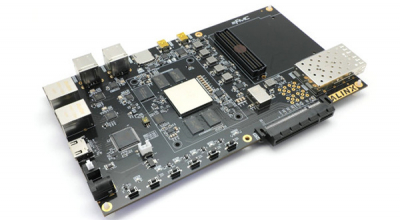

在本篇文章中,我们将介绍如何使用 Vitis 在 Alveo 板卡上开发和部署硬件加速应用。包括可用资源及文档,如何安装所需的开发工具和软件包,以及如何使用赛灵思 Github 加速用例。视频演示部分会向大家详细展示如何使用 Vitis 图形化界面和命令行流程在 Alveo U200 板卡上进行加速用例的开发和部署