ZYNQ入门实例——定时器中断与程序固化

judy 在 周二, 03/24/2020 - 09:32 提交

APU系统中CPU以串行执行代码的方式完成操作,软件方式很难做到精准计时,因此调用内部定时器硬件完成计时是更好的选择。本文以定时器中断方式控制LED周期性闪烁为例学习私有定时器的使用。同时学习如何将软件程序与硬件比特流文件一起固化到SD卡中,实现上电自动配置与启动自定义系统

APU系统中CPU以串行执行代码的方式完成操作,软件方式很难做到精准计时,因此调用内部定时器硬件完成计时是更好的选择。本文以定时器中断方式控制LED周期性闪烁为例学习私有定时器的使用。同时学习如何将软件程序与硬件比特流文件一起固化到SD卡中,实现上电自动配置与启动自定义系统

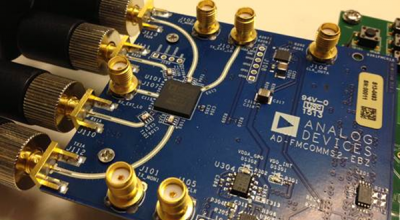

JESD204B是JEDEC委员会制定的一种串行接口标准,这种接口标准定义了数据转换器(ADC、DAC)和数字处理器(FPGA、 ASIC等)之间的数字信号传输方式。它作为第三代标准,补充了JESD204、JESD204A这前两代标准的不足之处。

Zynq® UltraScale+™ RFSoC ZCU216 评估套件配备第三代业界唯一单芯片自适应射频平台,是快速原型设计和 RF 应用开发的理想平台。该视频介绍了 ZCU216 评估套件提供的重要板载组件和配件。

神经网络中涉及到大量的张量运算,比如卷积,矩阵乘法,向量点乘,求和等。神经网络加速器就是针对张量运算来设计的。一个神经网络加速器通常都包含一个张量计算阵列,以及数据收发控制,共同来完成诸如矩阵乘法,卷积等计算任务

上一篇安装完相关程序后,这一篇就简单运行一个“Hello Vitis”的程序。本例硬件平台为ZYNQ平台,具体芯片为XC7Z035。ZYNQ 芯片分为 PL 和 PS, PS 端的 IO 分配相对是固定的,不能任意分配,而且不需要在 Vivado 软件里分配管脚,虽然本实验仅仅使用了 PS,但是还要建立一个 Vivado 工程,用来配置 PS 管脚

建立基于 zcu102 开发板的 Vivado 工程。建立 Block Design,添加 Zynq UltraScale+ MPSoc 的 IP。点击 Run Block Automation,自动配置 IP 模块。双击打开配置窗口查看 UART 0 和 UART 1 已按照 zcu102 开发板的硬件连接设置完成。

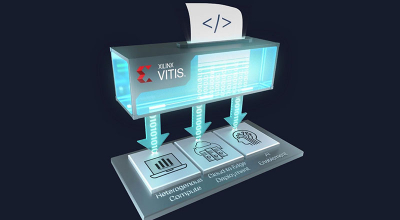

指导 SDK 用户如何将现有 SDK 项目迁移至 Vitis™ 统一软件环境

vitis虽然已经发布很长时间了,但是我就要尝鲜。。。首先是安装,本教程分两个主要的平台(WIN10和Ubuntu)给出安装教程和源文件。

ADC芯片会包含许多性能参数,而我们在选择ADC芯片时,其中有一项关键性的参数值得关注,即数字化的数据输出接口类型(the type of digital data output)。目前在高速ADC芯片中,使用最广泛的数据输出接口类型有3种

本篇文章来测试Tutorials中的第2个例子:Mixing C++ and RTL Kernels。该例子中进行了两个步骤的实验,分别是sw_emu和hw_emu,我这变还是会继续在硬件上直接测试。