AXI总线简介(一)

demi 在 周二, 12/17/2019 - 15:13 提交

AXI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA进行以数据为主导的大量数据的传输应用。

AXI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA进行以数据为主导的大量数据的传输应用。

状态机是许多数字系统的核心部件,是一类重要的时序逻辑电路。通常包括三个部分:一是下一个状态的逻辑电路,二是存储状态机当前状态的时序逻辑电路,三是输出组合逻辑电路。

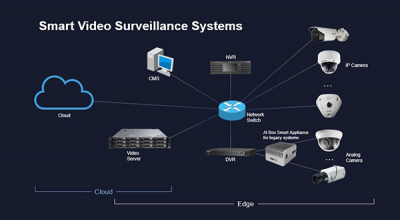

智慧城市将技术与基础设施汇集在一起,通过更高的安全性和效率来改善市民的生活。然而,大城市地区人口不断增加,加剧了城市在基础设施和保障市民安全方面面临多种挑战。再加上城市化人口流动性增强,长途远行逐渐成为家常便饭,我们显然需要更多的解决方案来改善现状。

PCIE 链路训练、枚举扫描、配置BAR的顺序?上电复位后,首先进行链路训练,之后进行枚举扫描、最后进行基地址寄存器BAR的配置。完成基地址配置后,就可以通过memory TLP读写进行寄存器的访问了。

本文档提供了为Xilinx®Zynq®UltraScale +™MPSoC器件设计和开发系统软件和应用程序所需的以软件为中心的信息。

本文主要介绍FPGA选型时的速度等级这个参数。大家在进行FPGA选型时都会看见一个参数:Speed Grade,这就是芯片的速度等级。

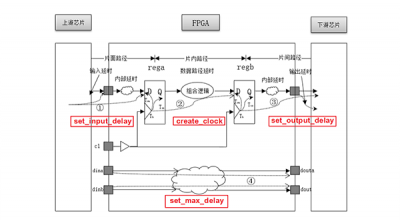

典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。

generate语句能够生成有规律的代码,较少语句数量,提高效率。

本文主要介绍Xilinx FPGA的FMC接口。Xilinx FPGA的FMC是FPGA Mezzanine Card的简称。FMC分为处理引擎(载卡)和I/O引擎(FMC模块)两大部分。

有多种类型的时序违例可归类为脉冲宽度违例:最大偏差违例;最小周期违例;最大周期违例;低脉冲宽度违例;高脉冲宽度违例。