【赛灵思开发者大会PPT下载】灵活应变的智能:从射频到核心网

demi 在 周四, 12/26/2019 - 13:00 提交

Adaptable Intelligence:From RF to the Core——灵活应变的智能:从射频到核心网 BY Liam Madden | 执行副总裁&有线及无线事业部 (WWG) 总经理

Adaptable Intelligence:From RF to the Core——灵活应变的智能:从射频到核心网 BY Liam Madden | 执行副总裁&有线及无线事业部 (WWG) 总经理

在rtl仿真中,x和z是两个情况,而在综合时被视为一种情况。因此在需要综合的代码中,是不允许出现x和z的。

赛灵思XDF合作伙伴方案介绍——eNCLUSTRA 基于Xilinx产品核心模块介绍

AXI协议是基于burst的,主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址。突发传输不能跨4KB边界(防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

Python中3个不可思议的返回——第一个:神奇的字典键;第二个:异常处理中的return;第三个:相同对象的判断。

时钟周期约束,顾名思义,就是我们对时钟的周期进行约束,这个约束是我们用的最多的约束了,也是最重要的约束。

重点介绍Versal Prime系列的一些关键特性,您可能是第一次听说Versal Prime系列,它是业界第一款自适应计算加速平台(ACAP),是以标量化、自适应、智能为特点的计算引擎。

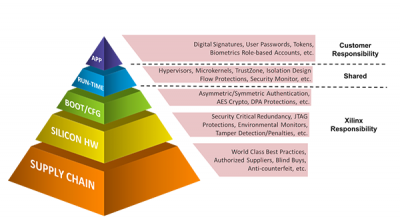

设计工程师的目标,希望仿真始终能够顺利进行。然而,在针对需要功能安全认证的市场进行设计时,必须注意掌控大局。这种情况下,设计任务就会比以往更复杂。市场营销与工程团队不仅面临着创造出优秀产品的压力,而且还必须考虑所有适用的安全标准,以确保产品能够满足某种需求。

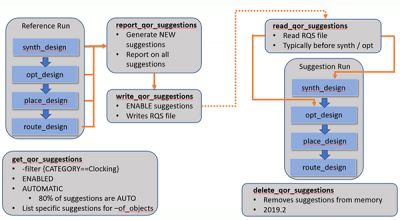

许多 FPGA 设计都难以达成所期望的性能目标。原因不尽相同,以下列出的只是其中部分可能的原因:未遵循 UltraFast 设计方法;时序约束不良;过高资源利用率;控制集过多;未采用最优化时钟设置;逻辑层次过多,难以达成目标性能;布局规划不良;布线拥塞;因约束导致工具优化受限。

Your Innovation Powered by Xilinx——赛灵思:创新的驱动力 BY Victor Peng | CEO 行政执行总裁