音视频图像处理技术高光聚焦:深维科技随赛灵思亮相深圳 LiveVideoStackCon 2019

demi 在 周日, 01/19/2020 - 10:27 提交

2019年12月13日,专业的音视频技术大会LiveVideoStackCon 2019第二场如期在深圳举行,赛灵思联合众多视频处理领域的合作伙伴共同为业界带来了精彩的演讲和实例演示。

2019年12月13日,专业的音视频技术大会LiveVideoStackCon 2019第二场如期在深圳举行,赛灵思联合众多视频处理领域的合作伙伴共同为业界带来了精彩的演讲和实例演示。

1 月 16 日,智能驾驶初创企业北京超星未来科技有限公司宣布与自适应和智能计算的全球领先企业赛灵思公司达成战略合作。双方将共同探索如何通过基于 FPGA、ACAP 芯片平台的AI技术推动智能驾驶发展,在全球范围内加速车规级安全、可靠的智能驾驶感控平台解决方案在主机厂及一级供应商中的应用落地。

UART是一种通用串行数据总线,用于异步通信。UART能实现双向通信,在嵌入式设计中,常用于主机与辅助设备通信。UART包括RS232、RS449、RS423等接口标准规范和总线标准规范,即UART是异步串行通信口的总称。

赛灵思 Zynq® UltraScale+™ MPSoC 支持 -3、-2 和 -1 速度等级,其中,-3E 器件性能最高。-2LE 和 -1LI 器件可以 0.85V 或 0.72V 的VCCINT 电压工作,专为实现更低的最大静态功耗而设计。使用以 VCCINT = 0.85V 工作的 -2LE 和 -1LI 器件时,L 器件的速度规格与 -2I 或-1I 速度等级相同。

归根结底,所有加速运行时都从根本上执行三个相关任务:内存分配,内存迁移和计算顺序。 在那把伞下隐藏了很多功能! 在本节中,我们将深入研究Xilinx运行时,以研究硬件加速的“软方面”的细微差别和表达能力。

本篇博文并非技术类文章,但无疑是专为技术人员撰写的。完成几个项目之后,您心知肚明这些项目能够一蹴而就或多或少都掺杂些运气成分。您可能会遇到人为错误、事先未曾预料到的困难、甚至是超出您控制的问题(比如,源端 (source) 或接收端 (sink) 设备的问题)。

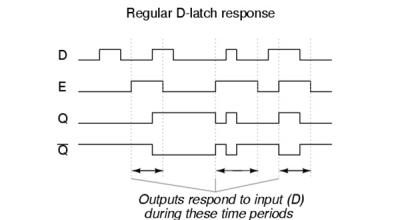

在FPGA的设计中,避免使用锁存器是几乎所有FPGA工程师的共识,Xilinx和Altera也在手册中提示大家要慎用锁存器,除非你明确知道你确实需要一个latch来解决问题。而且目前网上大多数文章都对锁存器有个误解,我们后面会详细说明。

锐文科技 CTO闫燕:由于带宽的提升,比如升到25G,甚至100G 的情况时,普通的CPU是没有办法满足网络上的业务的,它需要绑定几个CPU核来做网络加速。而我们的方案可以节省CPU的资源,把CPU本身做的网络上的业务卸载到FPGA里来做,从而大大提升CPU的效率。

不知不觉之中,大家发现可能机器(手机,电脑)可能比您自己更懂您,在您浏览网页和采购商品的时候,给您推荐的往往都很契合自己某一方面的特点和需求。这个变化就是得益于后台运行着的推荐算法。正因为有了 FPGA 强大的计算能力,让这样的海量检索与分析可以让互联网内容供应商以用户毫无察觉的速度将之付诸实现。

2020年1月15日,自适应和智能计算的全球领导者赛灵思公司(纳斯达克股票代码:XLNX)在位于北京市朝阳区安定路5号院的中海国际中心新办公室,举行赛灵思北京办公室乔迁庆典,隆重庆祝公司进驻新址。