FPGA系列之“速度等级”

demi 在 周一, 12/16/2019 - 15:14 提交

本文主要介绍FPGA选型时的速度等级这个参数。大家在进行FPGA选型时都会看见一个参数:Speed Grade,这就是芯片的速度等级。

本文主要介绍FPGA选型时的速度等级这个参数。大家在进行FPGA选型时都会看见一个参数:Speed Grade,这就是芯片的速度等级。

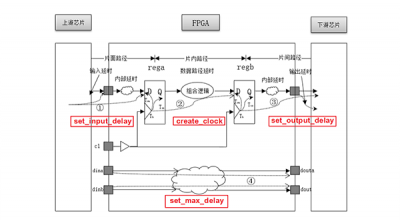

典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。

generate语句能够生成有规律的代码,较少语句数量,提高效率。

本文主要介绍Xilinx FPGA的FMC接口。Xilinx FPGA的FMC是FPGA Mezzanine Card的简称。FMC分为处理引擎(载卡)和I/O引擎(FMC模块)两大部分。

有多种类型的时序违例可归类为脉冲宽度违例:最大偏差违例;最小周期违例;最大周期违例;低脉冲宽度违例;高脉冲宽度违例。

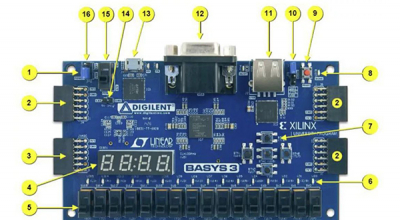

说起我和赛灵思的故事,可以追溯到3年前的大二。那时,我们精仪学院开设了数字电路设计课程,课程内容是学习数字电路知识,同时用FPGA进行实现。那是我人生中第一次接触FPGA,板子是Basys 3,板载一块小规模的赛灵思 Aritx-7 FPGA。第一次接触FPGA的感受是:怎么会有这么神奇的芯片?它全可配置、灵活性强,比之前用过的ARM芯片灵活多了!

2019年12月3日-4日赛灵思开发者大会( XDF )2019亚洲站在北京盛大揭幕。作为全球领先的FPGA异构计算加速方案供应商,北京深维科技隆重亮相此次峰会,向行业观众展示了超强算力的图像处理加速方案,从而为数据中心的解除“达摩克利斯之剑”提供了典型范本。

本文将先介绍三个VIVADO自带的视频输出通路相关的重要IP核,搭建一个比较简单的视频通路,为不久之后的摄像头到显示屏通路打下基础......

2019 年 12 月 3 日 - 4 日,赛灵思 XDF-亚洲站在北京国家会议中心举办,高效能服务器和存储技术国家重点实验室受邀做主题报告,对研究成果向国内外的与会代表进行展示交流。报告针对当前智慧金融异构加速领域的创新,向听众分享了实验室与 Xilinx 联合成立的“智慧金融科技创新国际联合实验室”的研究情况。

汽车应用作为赛灵思“加速核心市场发展”战略落地市场之一,本届 XDF-亚洲站的 75 场主题演讲和来自数十个现场生态伙伴展示中都有涉及,作为内行的您一定管中窥豹、看出门道了吧?今天,让我们一起来看看赛灵思专家毛广辉发自 XDF-亚洲站现场的点评吧~