让视频中的细节全部无所遁形 — Deepgreen DB 视频探测工具

judy 在 周四, 08/01/2019 - 10:42 提交

Deepgreen DB 视频发现工具是一款大规模并行 Postgres (MPP) 数据仓库平台,专门面向非结构化视频数据与结构化关系数据的大数据分析而设计。它通过编排大量 FPGA 加速节点,在执行复杂的汇总和比较操作的同时扫描大量数据,从而高效地解决复杂的分析问题。

Deepgreen DB 视频发现工具是一款大规模并行 Postgres (MPP) 数据仓库平台,专门面向非结构化视频数据与结构化关系数据的大数据分析而设计。它通过编排大量 FPGA 加速节点,在执行复杂的汇总和比较操作的同时扫描大量数据,从而高效地解决复杂的分析问题。

前两篇我们学习了UDP的发送,本文学习如何处理接收数据。lwIP为UDP接收提供了回调机制,学会回调机制的使用可以为学习更复杂的TCP回调打下基础。本文使用UDP设计一个echo服务器,开发板将来自所有IP地址和端口的数据原路发送回去,功能和SDK提供的“lwip echo server”例程一样,只不过例程使用的是TCP协议。

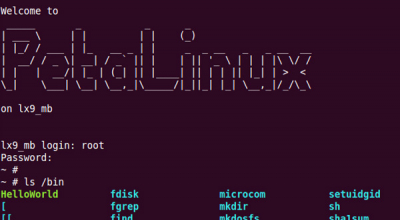

PetaLinux工程编译后,会生成很多临时文件,占用较大的硬盘空间。软件人员可能有很多PetaLinux工程。这种情况下,对于暂时不用的工程,可以删除其中build目录下的临时文件。下面三个脚本,可以搜索当前目录下的所有PetaLinux工程,并删除其中build目录下的临时文件。

8 月 23 日,在LiveVideoStackCon音视频技术大会北京站举行期间,作为大会铂金赞助的赛灵思公司,将联合生态合作伙伴,举办为时半天的 “Xilinx 视频加速技术研讨会”,并现场演示多种视频加速解决方案

作者:hankf,Xilinx Employee

独立编译VCU Ctrl-sw的办法

1. 安装PetaLinux

2. 导入PetaLinux环境

最近知名 IDE 厂商 JetBrains 发布了 2019 年开发者调查报告。本文汇总和 Python 相关的调查数据和结果

本能篇主要讲一下AXI GPIO 中断,AXI GPIO 中断也是共享外设中断的一种。本讲和上一讲说的中断很像,区别就是AXI GPIO 中断需要AXI GPIO核。

Laurent El Ghaoui 和 Serge Marquié

在Uber和Lyft之后,现在轮到Slack上市了。和任何申请公开上市的公司一样,Slack必须向SEC提交一份名为S1的特殊文件。S1文件旨在上市前, 向市场参与者提供有关公司结构,预计收入,客户获取,业务风险等信息。

下面向大家介绍了使用HLS封装的缩放IP来实现视频图像缩放功能。将HLS封装的缩放IP加入到OV5640图像传输系统,验证图像放大和缩小功能。

赛灵思今天宣布其人工智能平台Zynq UltraScale+ MPSoC ZCU104 评估套件在中国人工智能产业发展联盟(AIIA)主导的“AIIA DNN Benchmark”人工智能端侧芯片基准测试V0.5版本的第二轮测试测评中,囊括参测7个网络中板卡类6项性能冠军