一文了解“工业相机”

judy 在 周四, 08/08/2019 - 09:36 提交

工业相机有多种分类方法,比较常见有:按感光芯片的类型分CCD(电荷耦合器件)和CMOS(互补金属氧化物半导体),根据输出色彩分为黑白和彩色,按像元的排列方式可分为线阵和面阵,按成像维度可为二维(2D)和三维(3D)等。本文将针对这四类分法,研究和讨论工业相机的基本原理及技术发展

工业相机有多种分类方法,比较常见有:按感光芯片的类型分CCD(电荷耦合器件)和CMOS(互补金属氧化物半导体),根据输出色彩分为黑白和彩色,按像元的排列方式可分为线阵和面阵,按成像维度可为二维(2D)和三维(3D)等。本文将针对这四类分法,研究和讨论工业相机的基本原理及技术发展

本次研讨会将为所有医疗设备的架构师和设计人员介绍一种可适用于所有工业自动化,以及其他高可靠性应用的功能安全策略和网络安全方法,同时还将介绍赛灵思的方案是如何应用于基于风险管理的意料设备设计流程中的,从而帮助客户创建更稳健的设计,加快上市时间

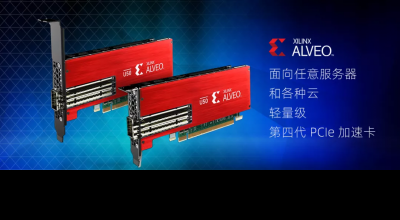

Alveo™ U50 加速卡今天终于可以与大家见面了。Alveo U50 加速卡是业界首款可以支持第四代PCIe ( PCIe Gen 4) 的轻量级自适应计算加速卡, 专门为扩容各种不同关键计算、网络和存储工作负载而特别设计,而且所有的加速都在同一个可重配置 FPGA 平台之上实现

从前面几个UDP的程序实例中我们可以体会到pbuf的重要性,对pbuf的灵活操作也是完成程序功能和提高代码效率的关键。本篇总结lwip的pbuf.c中的常用函数并给出示例程序,其中部分函数和string.h文件中提供的传统内存操作函数功能相同

赛灵思 Alveo™ U50 数据中心加速器卡为金融计算、机器学习、计算存储以及数据搜索和分析领域的工作负载提供优化加速功能。U50 基于赛灵思 UltraScale+™ 架构,采用高效的 75 瓦封装,外形小巧,U50 包括 带宽为 460GB/s 的 HBM2,100GbE 网络和 PCI Express 4.0,专为部署在任意服务器上而打造

今天赛灵思再宣布推出 Alveo™ U50,进一步扩展 其Alveo 数据中心加速器卡产品组合。Alveo U50 卡是业界首款可以支持第四代PCIe ( PCIe Gen 4) 的轻量级自适应计算加速卡, 特别为单个可重配置的 FPGA 平台就能大幅加速各种不同的关键计算、网络和存储工作负载而设计

本指南介绍Xilinx Zynq UltraScale+RFSoC特性套件的组件,功能和操作。

这篇文章介绍一种不同于针对压缩单个权重的方法:多个权重数据组合为向量,将向量视为一个整体,映射到其他向量空间,完成压缩。作者在resnet-50上做了实验,将100MB权重压缩到了5MB(实现了20倍压缩比例),同时在imageNet上测试的top-1精度保持的很好(76.1%)

数据类型

基本数据类型:

整型(int),浮点型(float),字符串(str),列表(list),元组(tuple),字典(dict),集合(set),布尔(bool)

数值类型(整数,浮点,布尔)

序列类型(字符串,列表,元组)

散列类型(字典,集合)

FPGA为什么是可以编程的?恐怕很多菜鸟不知道,他们也不想知道。因为他们觉得这是无关紧要的。他们潜意识的认为可编程嘛,肯定就是像写软件一样啦。软件编程的思想根深蒂固,看到Verilog或者VHDL就像看到C语言或者其它软件编程语言一样。一条条的读,一条条的分析