FPGA与ADC的SPI配置实战篇(3)——AD9249三线SPI配置

judy 在 周二, 08/06/2019 - 08:48 提交

本篇咱们继续以ADI公司的多通道高速ADC—AD9249为实例,向大家演示FPGA是如何通过SPI协议向该ADC读写寄存器配置数据的。如下图所示为AD9249的功能框图,其为16通道、65MSPS、14bit精度的多通道高速ADC,且其SPI接口只为三线模式

本篇咱们继续以ADI公司的多通道高速ADC—AD9249为实例,向大家演示FPGA是如何通过SPI协议向该ADC读写寄存器配置数据的。如下图所示为AD9249的功能框图,其为16通道、65MSPS、14bit精度的多通道高速ADC,且其SPI接口只为三线模式

在本次直播课程当中,我们将向您详细讲解及演示,基于赛灵思的加速方案是如何帮助客户实现从传统 ADAS 方案演变为更多基于机器学习和 AI 的自动驾驶的。

网络压缩在AI加速中可以说起到“四两拨千斤”的作用,网络参数的减小不仅仅降低了存储和带宽,而且使计算逻辑简单,降低了LUT资源。从本篇开始,我们就一起挖掘一下网络压缩算法的类型,原理,实现,以及效果。写这类算法类文章,一是学习,二是希望能够令更多做FPGA的人,不再将眼光局限于RTL,仿真,调试,关心一下算法,定会发现FPGA的趣味和神通

由东南大学、赛灵思电子科技(上海)有限公司(Xilinx)、南京集成电路产业服务中心(ICisC)联合主办的2019 SEU-XILINX暑期学校完美落幕啦! 在7月7号到7月19号的2周时间之内,通过2次测试,7场专题讲座和7天项目开发的经历,让来自于国内、澳门地区和海外71所高校合计110名学员学习和实践了FPGA设计技巧和各种各种工具结合下的智能应用

使用前,执行命令source /opt/Xilinx/SDK/2019.1/settings64.sh ,导入相关路径,就可以。

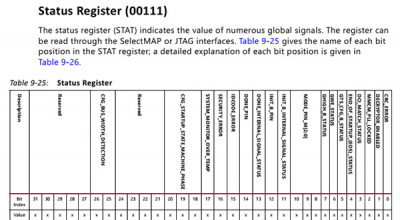

Xilinx的FPGA有多种配置接口,如SPI,BPI,SeletMAP,Serial,JTAG等;如果从时钟发送者的角度分,还可以分为主动Master(即由FPGA自己发送配置时钟信号CCLK)和被动Slave(即由外部器件提供配置所需要的时钟信号);另外还可由板上稳定晶振提供时钟信号,经由FPGA的EMCCLK接口,再从CCLK端口送出

本篇文章,我们将从与自动驾驶的关系、加速中遇到的挑战、量化计算、节约资源和带宽五个方面,介绍 ACU-Advanced 的核心高性能芯片 FPGA 的相关技术。这是一篇“硬核”的技术文章。正是这些后台的“硬核”技术,成就了令人炫目的自动驾驶。本文中介绍的相关技术已经落实在 Valet Parking 产品中的量产 ACU 硬件上。

在JESD204C入门系列的 第1部分 中,通过描述它解决的一些问题,对JESD204标准的新版本进行了说明。通过描述新的术语和特性来总结B和C版本标准之间的差异,然后逐层概述这些差异。因为第1部分已经奠定了理解基础,现在我们来进一步研究一下JESD204C标准几个更值得注意的新特性

本文首先说明了PL开发的完整流程,再对仿真和调试功能进行单独说明。

当赛灵思确定公司未来的重点将是实现数据中心加速,以及从芯片供应商转变为提供下一代平台公司的时候,赛灵思高层执行团队就已经在着手确定和物色可以支撑这些战略的关键技术和可以提供这些关键技术的企业,而Solarflare 公司就在我们的候选名单之中