Xilinx 7系列FPGA分类简介

judy 在 周一, 05/27/2019 - 10:02 提交

赛灵思公司的7系列FPGA根据不同客户的应用需求,分为4个子系列,即Spartan7系列、Artix7系列、Kintex7系列以及Virtex7系列。和前几代FPGA产品不同的是,7系列FPGA采用的是统一的28nm设计架构,客户在不同子系列的使用方式上是统一的,消除了不同子系列切换使用带来的不便

赛灵思公司的7系列FPGA根据不同客户的应用需求,分为4个子系列,即Spartan7系列、Artix7系列、Kintex7系列以及Virtex7系列。和前几代FPGA产品不同的是,7系列FPGA采用的是统一的28nm设计架构,客户在不同子系列的使用方式上是统一的,消除了不同子系列切换使用带来的不便

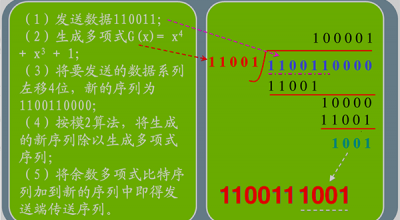

CRC校验的原理非常简单,其中,生成多项式是利用抽象代数的一些规则推导出来的,而模2加(也就是异或),是对应于有限域的除法。

Xilinx 可使服务器通过工作负载优化,以类似 CPU 和 GPU 方案的 1/10 时延及功耗实现 10 倍吞吐量。应用通过 OpenCL、C、和 C++ 等语言编写。灵活的、基于标准的解决方案,融软件可编程能力、负载优化、和高性能数据中心互联为一体, 并与保密性紧密结合在一起,以满足下一代云计算的需求

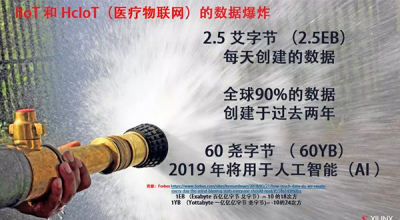

近些年来,物联网的发展为工业和医疗领域带来了新的活力。由此,也催生了工业物联网(IIoT)和医疗物联网(HcIoT)的创新。这些新兴领域的崛起,为FPGA的发展提供了机会。作为FPGA业界的佼佼者,赛灵思在工业物联网和医疗物联网领域上的表现如何?

为进一步提升电子信息类工程人才培养质量,拓展产学研协同育人模式,培养掌握行业先进技术平台并具有创新设计和工程实践能力的大学毕业生,在新工科产学研联盟的指导下,由东南大学、赛灵思公司(Xilinx)、南京集成电路产业服务中心(ICisC)联合主办,于2019年7月举办面向海内外高校在校大学生和研究生的“2019年SEU-Xilinx国际暑期学校”。

视频展示了基于赛灵思产品的灵活的 5G xHAUL 传输,以及灵活应变的 xPONZ 解决方案。

敢问工厂和医院,在今天这样一个万物互联的物联网时代,在人工智能几乎无处不在的时代, 你准备好升级了吗?今天 ,我们就来听听赛灵思工业、视觉、科学与医疗市场总监 Chetan Khona 如何看待人工智能在工业和医疗领域的发展,在产业升级和变革的关键时刻如何做正确的选择,而且未雨绸缪,让今天的选择同样能够适应未来的再升级、再发展

启动XEN后,测试ZDMA应用程序, 检查DMA的secure模式。打算在XSCT下读取寄存器 slcr_gdma。如果target选择A53 #0,不能读取寄存器 slcr_gdma。如果target选择PSU,能读取寄存器 slcr_gdma。

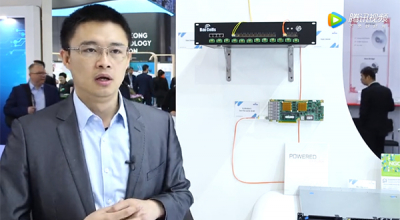

佰才邦公司在本届 MWC 展会上展示了其用于 NR加速和同步的PCIe加速卡,可适用于 O-RAN 以及 TIP Open RAN,同时现场还展示了他们的用于室内的O-RAN射频Hub。

在这篇文章中,我们将介绍如何调用 Hyperlynx®、如何设置简单的原理图以及如何运行一些基本的仿真操作。Hyperlynx® 可支持下列两种仿真工作流程。