20 个超棒的数据科学 Python 库

judy 在 周四, 05/23/2019 - 09:50 提交

为了方便学习,本文列出的20个Python库将按领域进行分类,有些你可能并不熟悉,但是真的能提高你的模型算法实现效率,多一点尝试,多一些努力!

为了方便学习,本文列出的20个Python库将按领域进行分类,有些你可能并不熟悉,但是真的能提高你的模型算法实现效率,多一点尝试,多一些努力!

Xilinx 面向数据中心的 SmartCORE IP 与 LogiCORE™ IP不仅有备有文件的、业经验证的 IP 核(可执行包括流量管理、数据包处理、TCP 卸载、密码、压缩和安全在内的复杂网络功能),而且还有包括 1G/10G/40G/100G 以太网 MAC、PCIe 2 代及 3 代、XAUI/XLAUI/CAUI、串行快速 I/O、SATA 和 SAS 在内的所有重要 I/O 接口,可为系统设计人员的项目提供先人一步的优势

为MPSoC编译Android 8的主要流程和命令

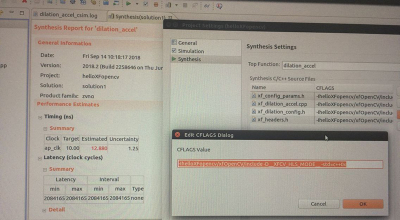

本来写了一篇关于在HLS中使用xfOpenCV的记录,一步一步,但不小心删掉了。只能重新大致回忆下,肯定没有之前的全面。

UART作为异步串口通信协议的一种,工作原理是将传输数据的每个字符一位接一位地传输。其中每一位(Bit)的意义如下:

过去 10 年来,云计算成为在全球范围内出现的的一个新兴市场,通过因特网为全球数十亿用户提供计算服务。云计算趋势的发展反映出人们使用计算机方式的根本变化。云技术可为企业提供新的方式,将任务从本地 IT 基础架构转移到优化的远程计算集群,同时也交到云服务供应商的手中

电路的核心逻辑是组合电路,比如异步的FIFO/RAM读写信号、地址译码信号等电路;电路的输出不依赖于某一个时钟,也就说不是由时钟信号驱动触发器产生的;异步电路非常容易产生毛刺,且易受环境的影响,不利于器件的移植;

数字化转型进入加速期,需要高效且灵活应变的系统,异构计算将大行其道,而FPGA堪当重任。IDC预计,到2021年至少50%的全球GDP将会是数字化的,中国数字经济的比重将超过55%。这表明数字化转型不再只是一个热词,已然进入加速期,全球也将进入数字经济时代。

在Ubuntu 16.04下,安装petalinux需要的软件包遇到错误,“requested an impossible situation”。安装Ubuntu 16.04时,选择的地区是上海。据说选择香港不会有这个问题。

本文简单介绍Zynq的中断系统和中断控制器。Zynq的PS部分基于ARM架构,使用了两个Cortex-A9处理器(CPU)以及GIC pl390中断控制器(单核Zynq则只有一个GIC)。GIC是通用中断控制器(Generic Interrupt Controller)的简称。双核的中断系统框图如下