MPSOC之6——开发流程linux编译

judy 在 周日, 09/30/2018 - 11:38 提交

0.顶层Makefile增加交叉编译器

顶层makefile:

ARCH ?= $(SUBARCH)

CROSS_COMPILE ?= $(CONFIG_CROSS_COMPILE:"%"=%)

0.顶层Makefile增加交叉编译器

顶层makefile:

ARCH ?= $(SUBARCH)

CROSS_COMPILE ?= $(CONFIG_CROSS_COMPILE:"%"=%)

您想缩短您产品的上市时间和开发费用吗?请来访我们的展台看我们是如何做到的。

Vivado Simulator基本操作

Vivado Simulator是一款硬件描述语言事件驱动的仿真器,支持功能仿真和时序仿真,支持VHDL、Verilog、SystemVerilog和混合语言仿真。点击运行仿真后,工具栏中显示了控制仿真过程的常用功能按钮:

什么是ttl电平

TTL电平信号被利用的最多是因为通常数据表示采用二进制规定,+5V等价于逻辑"1",0V等价于逻辑"0",这被称做TTL(晶体管-晶体管逻辑电平)信号系统,这是计算机处理器控制的设备内部各部分之间通信的标准技术。

一、AXI DMA介绍

【导读】Python在解决数据科学任务和挑战方面处于领先地位。而一些方便易用的库则帮助了开发人员高效开发。在这里我们整理了20个在深度学习、数据分析中最常用、最好用的Python库,供大家一起学习。

作者| ActiveWizards

编译|专知

整理|Yingying,李大囧

核心库与统计

本文是该系列的第20篇。数字水印是一种将标识信息嵌入到载体当中,且不影响载体使用的一种技术,主要分为时域水印嵌入算法(将水印嵌入到时域采样数据中)和变换域水印嵌入算法(先对音频做变换,将水印嵌入到变换域系数中)。本文将介绍一种简单的时域水印嵌入算法——LSB算法。

LSB算法

程序的格式框架

作者:liuwanpeng

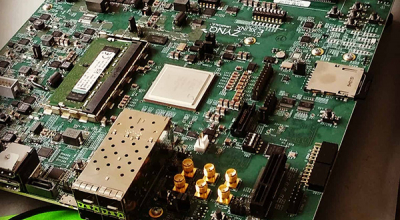

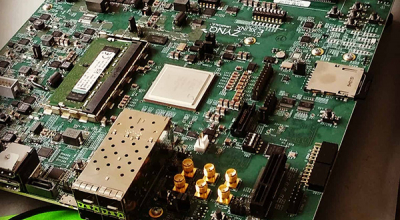

需要把若干文件打成大包,烧写到flash或者sd卡中,才能启动运行。

1.petalinux打包

petalinux-packet打包时,需要petalinux的工程,限制太死了,不用。

作者:张汉青;来源:经济参考报

作为2018世界人工智能大会聚焦技术的全球性论坛之一,全球异构计算高峰论坛9月19日在上海举办,受到了国内外业界的广泛关注。