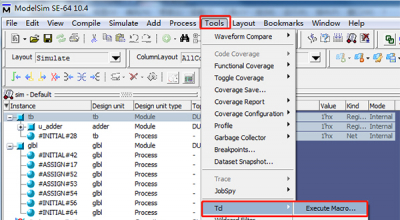

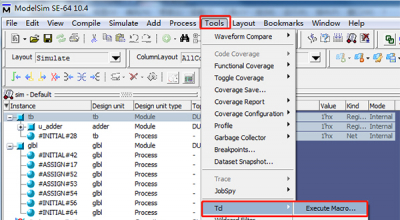

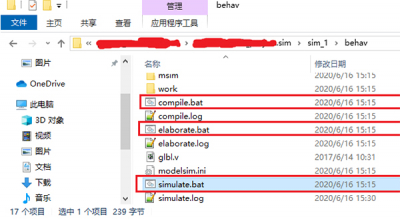

老鸟的姿势学起来,用脚本进行modelsim仿真

judy 在 周四, 02/17/2022 - 09:50 提交

老鸟的姿势学起来,用脚本进行modelsim仿真

老鸟的姿势学起来,用脚本进行modelsim仿真

Xilinx的原语OSERDESE2是一种专用的并-串转换器,每个OSERDESE2模块都包括一个专用串行化程序用于数据和3状态控制。数据和3状态序列化程序都可以工作在SDR和DDR模式。

IBUFDS、和OBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。IBUFDS 用于差分输入,OBUFDS用于差分输出。

有很多客户在比较 FFT C-Model 仿真和 FFTIP 前仿遇到问题。今天赛灵思技术专家对此提出三种原因和解决办法。

用户在用第三方仿真器对Vivado设计做仿真的时候,面临的第一个任务就是做仿真库的编译。事实上,后续相当一部分碰到的问题都与仿真库编译相关。今天,我们就来梳理一下关于仿真库编译的方方面面。

芯片设计从RTL代码一直到最后流片的GDSII文件,都是文本文件,因此,掌握文本分析处理语言是集成电路设计的一项重要的基本功。本文是孙义雯同学采用Python语言实现的Vivado和Modelsim联合仿真的自动化脚本,已经在实际项目中经过较长时间的检验,今天开源出来,供大家学习,欢迎留言交流心得体会和改进建议

Xilinx FIR IP的介绍与仿真

在仿真验证中,SV语言不能很好的描述复杂的计算或者流程关系,使用软件语言(比如C)就比较方便。那么当我们使用C描述了这些关系后,如何在基于SV的仿真环境中使用呢?有两种方式,一种是将C编译为可执行文件,利用系统函数进行调用。另

本答复记录涵盖在 HyperLynx 中创建 IBIS-AMI 仿真测试平台的步骤。以 UltraScale+ GTY IBIS-AMI 模型为例。本教程使用 HyperLynx VX.2.4。

赛灵思 AXI Verification IP (AXI VIP) 是支持用户对 AXI4 和 AXI4-Lite 进行仿真的 IP。它还可作为 AXI Protocol Checker 来使用。此 IP 只是仿真 IP,将不进行综合(它将在 Pass-through 配置中被连线所替代)。