【用户指南】探索 Versal ACAP 设计方法论

judy 在 周三, 03/17/2021 - 09:50 提交

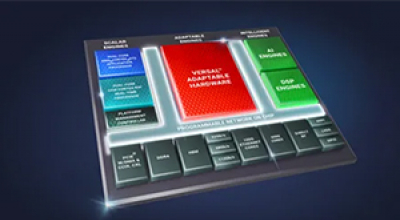

身处智能时代,科技发展日新月异,伴随数据中心、有线网络、5G 无线和汽车等愈加丰富的场景,相应的技术与功能也正经历飞速迭代,因此,单一计算架构已难以应对海量数据处理需求,赛灵思 Versal ACAP多核异构计算平台致力于帮助所有开发者保持即时的灵活应变能力。

身处智能时代,科技发展日新月异,伴随数据中心、有线网络、5G 无线和汽车等愈加丰富的场景,相应的技术与功能也正经历飞速迭代,因此,单一计算架构已难以应对海量数据处理需求,赛灵思 Versal ACAP多核异构计算平台致力于帮助所有开发者保持即时的灵活应变能力。

本文档旨在记述用于对赛灵思 FPGA 设计进行编程和调试的 Vivado® 工具。FPGA 编程包括从已实现的设计生成比特流文件和将此文件下载至目标器件。本文档还描述了如何进行设计调试,包括 RTL 仿真和系统内调试。

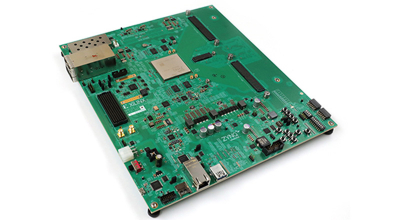

本文详细描述了 VCK190 评估板的功能。使用本指南开发和评估VCK190板上针对Versal ACAP XCVC1902器件的设计。

基于UltraScale架构的FPGA的封装和引脚规格不同。包括7系列FPGA在内的前几代产品。这些细节在此概述。

本指南描述了在 Vivado® Design Suite 中创建、打包和重用自定义 IP 的过程。详细介绍了如何使用创建和包装 IP 向导来包装自定义 IP,包括 IP 集成器中开发的 IP 和高级 IP 包装选项。

Zynq® UltraScale+™ RFSoC ZCU1275 特性描述套件提供您对集成型 ADC 和 DAC 以及 Zynq UltraScale+ XCZU29DR-2FFVF1760E RFSoC 上提供的 GTY 和 GTR 收发器进行特性描述和评估时所需的一切。

Xilinx VCU129评估套件设计用于Virtex UltraScale+™ XCVU29P-L2FSGA2577EES9818 FPGA,能够评估和开发56G PAM4应用。该评估套件设有多个常见的高速互连、板载存储器以及PCIe Gen 3接口。

Zynq® UltraScale+™ RFSoC ZCU208 评估套件是面向开箱即用评估及前沿应用开发的理想 RF 测试平台。该套件包含 UltraScale+ RFSoC ZU48DR,其集成 8 个 14 位 5GSPS ADC、8 个 14 位 10GSPS DAC 以及 8 个软决策前向纠错 (SD-FEC) 内核,专为快速启动 RF 类应用而设计。

Zynq® UltraScale+™ RFSoC ZCU216 评估套件配备业界唯一单芯片自适应射频平台,是快速原型设计和高性能 RF 应用开发的理想平台。ZCU216 评估套件配备 Zynq UltraScale+ RFSoC Gen 3 ZU49DR,可采用 16T16R 高速 RF-DAC 及 RF-ADC 实现 6GHz 以下频段的直接 RF 采样。

Vitis AI库是一组高级库和API,旨在通过深度学习处理器单元(DPU)进行有效的AI推理。 它基于具有统一API的Vitis AI Runtime构建,并且完全支持XRT 2019.2。