Vitis 统一软件平台文档

judy 在 周三, 12/20/2023 - 10:26 提交

本用户指南涵盖了 Vitis 入门、使用 Vitis Unified IDE、Bootgen 工具

本用户指南涵盖了 Vitis 入门、使用 Vitis Unified IDE、Bootgen 工具

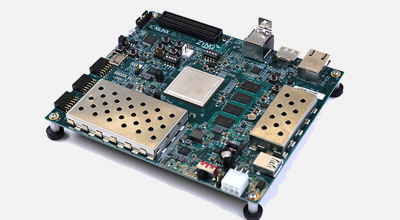

该视频分步说明了如何在 1 小时内在 Kria KD240 入门套件上实现加速应用

为硬件平台创建 PL IP 块、创建 PL 内核、功能仿真以及评估 AMD Vivado™ 时序收敛

AMD 将于11月28日,在北京举办今年度的技术盛会

Alveo UL3524 带来了7倍的时延提升 ,从而达到小于3纳秒的FPGA收发器时延

本文档旨在逐步指导您熟悉各种 Vitis 工具,这些工具采用自下而上的设计流程来开发系统组件

本文将探讨为何采用 8K 视频、其优势和潜在缺点

本文演示如何在 Zynq 设计中使用 Vitis 视觉库函数 (remap) 作为 HLS IP

该新系列非常适合需要低功耗和高 I/O 的成本敏感型应用,其面向广泛的行业