智算时代,合见工软数字验证全平台助力新质生产力效率加速

judy 在 周二, 01/14/2025 - 17:48 提交

合见工软验证产品市场总监曹梦侠介绍公司如何通过创新驱动的数字验证全平台完整解决方案,助力新质生产力效率的加速提升。

合见工软验证产品市场总监曹梦侠介绍公司如何通过创新驱动的数字验证全平台完整解决方案,助力新质生产力效率的加速提升。

1588V2时间同步协议广泛应用各个行业,尤其是新一代通信技术领域,对时间同步精度要求越来越高

第二代 AMD Versal AI Edge 系列自适应 SoC 的异构架构允许使用单芯片解决方案处理自动驾驶系统的所有阶段 —— 检测、感知、规划和执行

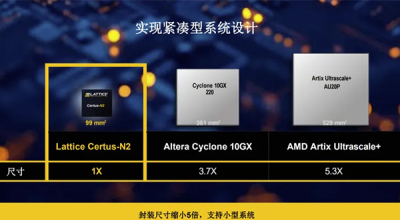

本文介绍了莱迪思Nexus 2平台在推出时与其他现有的同类FPGA的比较分析。分析包括功耗、启动时间、尺寸和安全特性

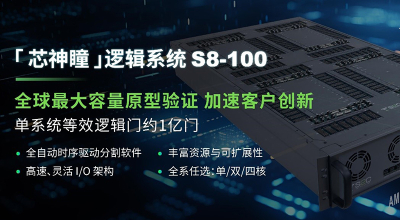

S8-100搭载了AMD自适应SoC——Versal™ Premium VP1902,单系统等效逻辑门约1亿门,容量较上代产品提升两倍,支持多系统级联

Versal器件的GTM支持PAM4电平,本文将介绍如何使用GTM仿真和观察PAM4信号。

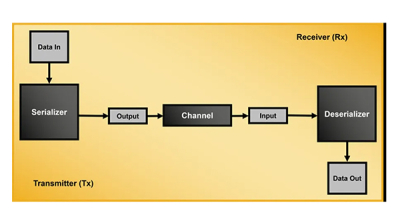

串行器/解串器(SERDES)是一种电子电路,用于将串行数据转换为并行数据,反之亦然,最常见于高速通信应用中

使用RFSoC(射频系统级芯片)制作适用于OTFS(正交时频空)信号的高动态时延多普勒信道模拟仿真器的原因

本文提供了基于2023.2 Vivado的参考工程,展示如何使用Microblaze 地执行(XIP)程序,并提供一个简单的bootloader。

本文基于此解释了卷积神经网络(CNN)及其对人工智能和机器学习的意义。