一种集成FPGA和DSP芯粒的异构系统级封装

judy 在 周二, 06/25/2024 - 15:41 提交

将多个异构芯粒集成在一起进行封装是一种具有广阔前景且成本效益高的策略,它能够构建出既灵活又可扩展的系统,并且能有效加速多样化的工作负载

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

将多个异构芯粒集成在一起进行封装是一种具有广阔前景且成本效益高的策略,它能够构建出既灵活又可扩展的系统,并且能有效加速多样化的工作负载

Versal器件里包含多种加密引擎,包括SHA-3/384 engine、AES-GCM engine、RSA engine和ECC engine。

在激光雷达中,使用FPGA实现TDC时需要手动约束进位链的位置。这里简单记录下。

MATLAB有几种索引样式,它们不仅功能强大、灵活,而且可读性强、表现力强。矩阵是 MATLAB 用来组织和分析数据的一个核心组件

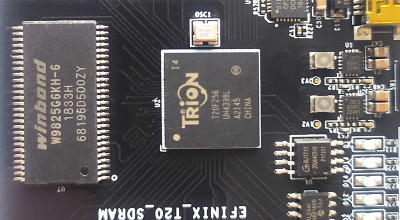

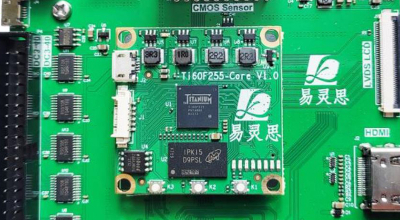

我们以T20F256为例来做一个实验。我们把T20F256的5个PLL全部打开,每个PLL的三路输出也全面打开。

本文从I2C协议的概述开始,描述协议的历史、不同速度模式、物理层和数据帧结构,最后介绍I2C混合电压系统中电平兼容性以及上拉电阻大小计算。

Interlaken协议的提出,既采用了高速串行传输,可配置多种线速率及物理层通路,同时继承了SPI-4.2通道化的数据包机制。

这里以钛金的LVDS为例。LVDS时钟的接收要连接名字为GPIOx_P_y_PLLINz名字的差分对,这样的管脚直接驱动PLL

Cadence 在 PCI-SIG DevCon 2024 上展示了使用现成部件达到每秒 128 千兆传输 (GT/s) 的PCIe 7.0 连接。

消除障碍,助力创新。Quartus® Prime专业版软件v24.1针对Agilex™ 5 FPGA E系列设备提供免费许可支持,助力零成本推动创新!