浅谈FPGA的配置引脚以及配置过程

judy 在 周二, 08/27/2024 - 17:25 提交

FPGA的配置引脚和配置过程是实现FPGA编程的关键部分。在配置过程中,FPGA从外部存储器或主机设备读取配置数据

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

FPGA的配置引脚和配置过程是实现FPGA编程的关键部分。在配置过程中,FPGA从外部存储器或主机设备读取配置数据

在调试模式下,可以通过JTAG下载MPSoC PL的bit文件,再下载MPSoC PS的软件。

AMD Xilinx的Versal器件中的PCIe IP,也可以作为PCIe Host。 AR76647 提供了相关驱动。

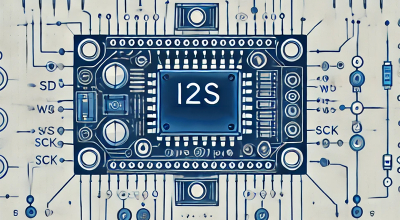

本文介绍了I2S收发器的配置与实现,用于FPGA的VHDL编程。

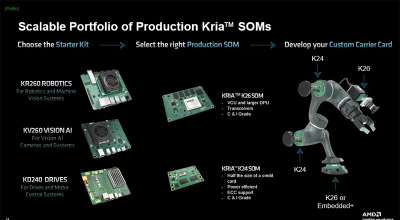

边缘端的传感器和连接设备的数量每天都在以指数级速度持续增长。连接数字计算设备的模拟电子传感器使系统能够获得态势感知并优化性能

PRBS误码测试时,通常需要计算误码率。如果使用IBERT,误码率可以在Vivado的GUI界面中读取

在PCIe(Peripheral Component Interconnect Express)总线系统中,复位信号是确保系统可靠启动和正常运行的重要机制。PCIe总线的复位主要有以下四种类型

一位客户向我们提出了一个想法,希望我们设计一种解决方案,用于监测无线通信信号的频谱,以确保系统安全,即检测频谱中的意外活动

本系列文章从数字芯片设计项目技术总监的角度出发,介绍了如何将芯片的产品定义与设计和验证规划进行结合,详细讲述了在FPGA上使用IP核来开发ASIC原型项目时

本调查介绍了 CXL,包括 CXL 1.0、CXL 2.0 和 CXL 3.0 标准。我们将进一步调查 CXL 的实现情况,讨论 CXL 对数据中心环境的影响以及未来的发展方向