Zynq UltraScale+ MPSoC:软件开发者指南 (v2021.2)

judy 在 周四, 11/11/2021 - 15:11 提交

本指南总结了使用 Xilinx® Zynq® UltraScale+™ MPSoC 器件进行设计所需的以软件为中心的信息。

为智能硬件开发者、创客提供有关英特尔嵌入式处理器的相关文档、软件包、开源文档资料

本指南总结了使用 Xilinx® Zynq® UltraScale+™ MPSoC 器件进行设计所需的以软件为中心的信息。

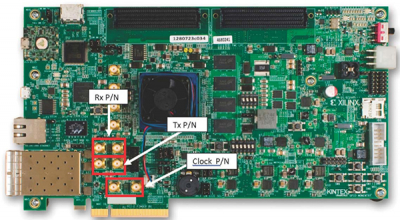

本文描述了一种使用 Xilinx器件和 PICXO 的技术,该技术去除了外部 PLL 电路以允许 SDI 视频输出与输入 HSYNC 时钟同步。

本文提供一个系统,旨在通过利用千兆位收发器内的功能取代外部压控晶体振荡器(VCXO)电路。

本应用说明讨论了如何使用新颖的全数字压控晶体振荡器(VCXO)替代技术,利用Virtex-6 FPGA实现锁频的三倍速率直通设计。该设计完全在Virtex®-6 FPGA内部实现。

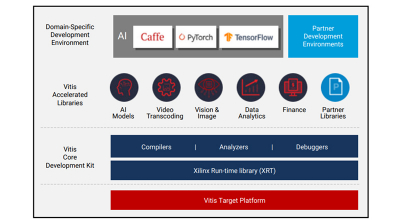

Kria KV260视觉AI入门套件是一个开箱即用平台,开发人员可以通过首选设计环境,在任何抽象层添加定制和差异化功能,包括应用软件、AI模型乃至FPGA设计。本文描述了Kria™ KV260 Vision AI启动套件。

本文提供一个系统,旨在通过利用每个串行千兆位收发器内的功能来取代外部压控晶体振荡器(VCXO)电路。

本文提出了一种在现场可编程门阵列(FPGA)上生成真随机数的新方法,该方法以 多级反馈环形振荡器(MSFRO) 的随机抖动为熵源。在传统环形振荡器的基础上,增加了多级反馈结构,扩大了时钟抖动的范围,提高了时钟采样频率和熵源的随机性。与传统的时钟采样结构不同,我们利用MSFRO产生的时钟抖动信号对FPGA的锁相环(PLL)产生的时钟信号进行采样。

本文描述了两个ML建模应用,用于提高Vivado® ML版中时序延迟和路由拥塞估计的准确性。

本应用说明提供了一个系统,该系统旨在通过利用每个串行千兆位收发器内的功能来取代外部压控晶体振荡器(VCXO)电路。

本文描述了Vivado®设计套件中使用的电路设计元素,并与带有AI内核的Versal™ ACAP器件相关。元素细节包括VHDL和Verilog实例化代码、原理图符号、真值表以及设计元素的其他特定信息。