Vitis Model Composer 用户指南 (v2021.1)

judy 在 周五, 10/22/2021 - 14:44 提交

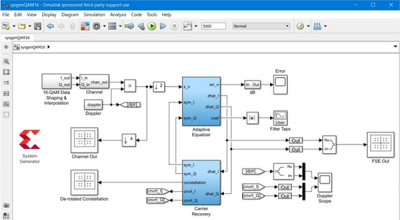

本文描述如何执行基于模型的设计,在 Simulink 环境中实现快速设计探索,并通过自动代码生成加速 Xilinx 器件的生产路径。

为智能硬件开发者、创客提供有关英特尔嵌入式处理器的相关文档、软件包、开源文档资料

本文描述如何执行基于模型的设计,在 Simulink 环境中实现快速设计探索,并通过自动代码生成加速 Xilinx 器件的生产路径。

对于任何一项设计,要想尽可能实现最低的功率包络,都需要在设计周期早期准确估算功耗。早期估算有助于选择合适的器件、充分发挥架构优势、更改设计拓扑,以及使用不同 IP 块。在设计阶段早期妥善权衡取舍,可以帮助用户在满足规格要求的同时,将自身产品更快速推向市场。本文档旨在介绍如何根据 Versal™ ACAP 架构的描述来使用 Xilinx Power Estimator (XPE)。

本文描述 Xilinx® Runtime (XRT) 的发布。

赛灵思 Versal™ 自适应计算加速平台 (ACAP) 设计方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。鉴于这些设计的规模与复杂性,因此必须通过执行特定步骤与设计任务才能确保设计每个阶段都能成功完成。本指南将分为以下五大章节,遵循指南里的步骤和最佳实践进行操作,将有助于您以尽可能最快且最高效的方式实现期望设计目标。

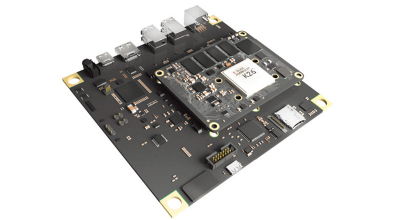

赛灵思 Kria SOM 采用基于加速应用的独特方法,为基于软件的设计提供了全新范例,同时还能助力工业、视觉、医疗与科学市场的应用保持系统级灵活性和 FPGA 性能优势。

Kria™ 机器人堆栈 (KRS) 是一组集成的机器人库和实用程序,它们使用硬件来加速工业级机器人解决方案的开发、维护和商业化。它采用 ROS 2 作为软件开发工具包 (SDK),并提出了一种以 ROS 2 为中心的开发方法,涵盖从计算图的创建到 Xilinx App Store 中的 ROS 2 覆盖工作区的商业化。

本文描述了在Vivado IDE环境中使用MATLAB和Simulink的DSP附加组件。

本文记录了Vivado®使用设计运行策略和单个实现命令进行放置和路由的实现功能。详细介绍了用于快速修改现有设计的增量编译流程,以及对信号路由路径进行精确控制的手动路由方法。

体现 Versal 器件价值主张的参考设计。平台设计包括针对不同市场的视频、机器学习和基于 100G 以太网的 IP。用户可以按原样使用这些设计,也可以根据应用需求对其进行修改。

Versal™ 自适应计算加速平台 (ACAP) 将标量引擎 (Scalar Engine)、自适应引擎 (Adaptable Engine) 和智能引擎(Intelligent Engine) 与领先的存储器和交互技术有机结合,从而为任何应用提供强大的异构加速功能。Versal 架构 PCB 准则已基于前几代进行了精简,以方便 PCB 布局专业人员和硬件设计师使用。