【下载】非整数数据恢复单元应用说明(v1.0)

judy 在 周二, 04/27/2021 - 16:27 提交

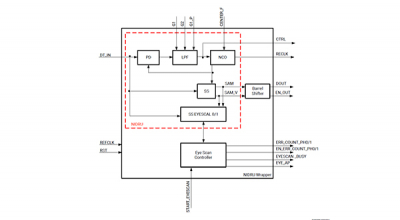

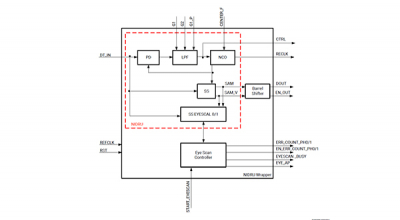

本文描述了Versal™ ACAP的一个非整数数据恢复单元(NIDRU)。NIDRU将较低的数据速率限制扩展到0 Mb/s,并允许SelectIO作为时钟和数据恢复单元运行。

为智能硬件开发者、创客提供有关英特尔嵌入式处理器的相关文档、软件包、开源文档资料

本文描述了Versal™ ACAP的一个非整数数据恢复单元(NIDRU)。NIDRU将较低的数据速率限制扩展到0 Mb/s,并允许SelectIO作为时钟和数据恢复单元运行。

本电子书重点介绍了Xilinx Zync® UltraScale+™ RFSoC,一个可扩展至完全支持6GHz以下频段的单芯片自适应无线电平台。此高性能RFSoC支持雷达、5G和卫星通信等RF无线解决方案所需的低功耗、高性能等特性。Zynq UltraScale+ RFSoC ZCU111评估套件旨在评估UltraScale+ ZCU28DR器件,并提供全面的射频模数信号链原型平台。

本文详细介绍Vivado工具对FPGA设计进行逻辑和时序分析的特点,以及工具生成的报告和信息。讨论实现时序收敛的方法,包括审查时钟树和时序约束,设计底层规划,以及平衡运行时间和结果。

本文描述了Vivado仿真器作为独立工具和Vivado设计套件的一部分的使用,以及使用波形查看器来分析和调试设计。记录RTL设计的行为仿真,以及综合和实现设计的功能和时序仿真。

本文详细介绍了使用Vivado®合成将RTL设计转化为门级网表,以便在Xilinx FPGA中使用SystemVerilog、Verilog和VHDL实现。描述了Vivado综合在项目和非项目模式中的使用,采用多种综合策略和设计约束。

本文描述在Vivado®工具中使用Xilinx®设计约束(XDC)。XDC结合了行业标准的Synopsys设计约束(SDC)和Xilinx专有约束。创建XDC来定义时钟,I / O延迟和时序异常(如错误和多周期路径以及最小/最大延迟)的详细信息。

本文介绍 Vivado® 集成设计环境 (IDE),它提供了直观的图形用户界面 (GUI),用于可视化和与 FPGA 设计交互。描述了Vivado IDE如何帮助您配置工具选项、分析和完善时序,以及设计平面图以改进结果。

本文详细介绍Vivado工具中Tcl脚本的使用,查询和修改自定义流程的内存设计。讨论如何使用Tcl过程来定义和共享自定义命令。提供了遍历设计层次结构、访问设计对象和处理自定义报告的步骤。

在赛灵思推出的 Zynq UltraScale+ MPSoC白皮书中,详细解读了基于 InFO 封装的全新 Zynq UltraScale+ MPSoC 如何实现紧凑型工业摄像头,并全面展现了其所具备的优秀的性能、功耗比等优势。

本文描述了使用 Vivado工具为 7 系列 FPGA 生成和编程加密位流和加密密钥的过程。