【下载】Xilinx器件上的深度卷积优化白皮书(v1.0)

judy 在 周一, 03/01/2021 - 15:23 提交

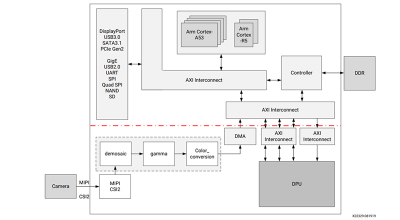

本白皮书探讨了深度卷积深度学习操作在Xilinx自适应设备上实现。 本白皮书旨在提供针对不同Xilinx器件的多种优化策略,以满足各种任务要求。 在边缘方面,Xilinx实现了轻量级的深度卷积引擎,该引擎支持相应的计算要求。

为智能硬件开发者、创客提供有关英特尔嵌入式处理器的相关文档、软件包、开源文档资料

本白皮书探讨了深度卷积深度学习操作在Xilinx自适应设备上实现。 本白皮书旨在提供针对不同Xilinx器件的多种优化策略,以满足各种任务要求。 在边缘方面,Xilinx实现了轻量级的深度卷积引擎,该引擎支持相应的计算要求。

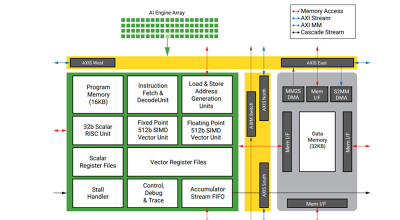

本文描述了Vitis™ AI开发包,这是一个用于深度学习处理器单元(DPU)的全栈深度学习SDK。

本文描述了用于卷积神经网络的 DPU。

本文重点介绍在Xilinx® Versal™ AI Core器件中使用AI Engine技术的数字下变频链(DDC)设计。展示了一种将DDC功能映射到AI Engine阵列的创新方法,利用Versal ACAP的独特架构来提供高性能和高效率。

本应用说明提供了使用与标准FPGA I/O耦合的外部硬件的FPGA MIPI D-PHY解决方案。

本指南提供新版本的 Vivado® Design Suite 概述,包括有关新增功能和功能变更信息、软件安装需求以及许可信息。其中还提供了已知问题列表,并包含指向可提供最新信息的答复记录的链接。

本文描述了如何在Versal™设备上使用高级I/O向导构建源同步高速I/O接口。

本文档旨在记述用于对赛灵思 FPGA 设计进行编程和调试的 Vivado® 工具。FPGA 编程包括从已实现的设计生成比特流文件和将此文件下载至目标器件。本文档还描述了如何进行设计调试,包括 RTL 仿真和系统内调试。

本指南详细描述了VMK180评估板的功能。使用本指南开发和评估VMK180板上针对Versal™ ACAP XCVM1802器件的设计。

本文提供有关 Versal™ ACAP 集成块 for PCI Express® 内核的详细信息,IP 性能和资源利用率数据。