【白皮书】在 FPGA 上部署 5G NR 无线通信

judy 在 周一, 11/02/2020 - 10:39 提交

本白皮书通过一个 5G NR 小区搜索设计来说明该过程,介绍将 MATLAB® 算法和 Simulink® 模型直接转换为适用于 FPGA 的 HDL 的工作流。

为智能硬件开发者、创客提供有关英特尔嵌入式处理器的相关文档、软件包、开源文档资料

本白皮书通过一个 5G NR 小区搜索设计来说明该过程,介绍将 MATLAB® 算法和 Simulink® 模型直接转换为适用于 FPGA 的 HDL 的工作流。

CLLM 4.0 是在 Xilinx Alveo 板上运行的硬件加速低延迟消息传递解决方案。

本文介绍如何将低功率域 (LPD) 作为一个通道和 PL 中的一个三模冗余 MicroBlaze 来创建和实现单片通用 2 通道系统。

在单个器件中集成安全/非安全功能成为可能。Xilinx提供当今一流的工具和技术,使IEC/ISO安全认证成为可能。

本指南描述了在 Vivado® Design Suite 中创建、打包和重用自定义 IP 的过程。详细介绍了如何使用创建和包装 IP 向导来包装自定义 IP,包括 IP 集成器中开发的 IP 和高级 IP 包装选项。

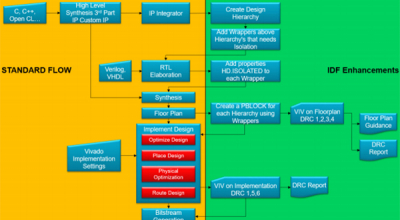

Zynq UltraScale+ 的隔离设计流程主要介绍如何使用支持 Xilinx Vivado 设计套件的 Xilinx IDF 实现安全关键型设计。

从 Vivado 2018.3 开始,Vivado 隔离验证器 (VIV) 将与 Vivado 版本集成,支持 UltraScale+ 器件(包括 Zynq UltraScale+)。本文档主要介绍如何在 FPGA/PL 设计中使用新的 Vivado 隔离验证器 (VIV) 来验证隔离。

Integrated Block for PCIe® 核是高可靠性、高带宽、高可扩展性的串行互连构建块,适合与 UltraScale+™ 器件配合使用。该核可对 UltraScale+ 器件中提供的集成块进行例化。

本指南描述了嵌入式设计中的系统性能监控。

决策树加速器可加速梯度提升树和随机森林算法的推断进程。它能够与通过 XGBoost、LightGBM、Scikit 学习、H2O.ai 和 H2O 无人驾驶 AI 创建的模块协同工作。该软件允许数据科学家和工程师构建快速、可扩展的高成本效益机器学习基础架构,无需改变机器学习框架的使用