GRegeX 12.8GB/s解决方案

judy 在 周四, 08/27/2020 - 10:35 提交

正则表达式是特殊编码的文本字符串,用作匹配字符串集的模式。GRegeX 是一个在 FPGA 芯片上实现标准正则表达式算法的实现方案,可使用单个 IP 核实现 12.8 Gb/s 的吞吐量。

为智能硬件开发者、创客提供有关英特尔嵌入式处理器的相关文档、软件包、开源文档资料

正则表达式是特殊编码的文本字符串,用作匹配字符串集的模式。GRegeX 是一个在 FPGA 芯片上实现标准正则表达式算法的实现方案,可使用单个 IP 核实现 12.8 Gb/s 的吞吐量。

本应用说明介绍了选择串行外设接口(SPI)闪存作为Xilinx 7系列FPGA的配置存储器存储的优势以及实现该解决方案的细节。

Grovf 现在提供其卸载引擎 Hyperon,它是一组在 FPGA 芯片上实现的基本编程算法,与简单易用的主机驱动程序集成。Hyperon 提供算法的加速版本,例如:正则表达式(RegEx,几乎完全支持)、文本相似性匹配、搜索、排序、线性代数(矩阵转置、点积、范数平方、矩阵相乘)以及无损数据压缩等

此参考设计采用 TPS53681 多相控制器和CSD95490Q5MC 智能功率级,可实现为 Xilinx Virtex Ultrascale+ FPGA 的 0.85V、200A VCCINT 轨供电的高性能设计。该控制器的次级输出可用于为FPGA 的辅助轨供电。智能功率级和集成 PMBus便于轻松设置输出电压和遥测关键设计参数

Memcached 是一款高性能内存对象高速缓存系统,由 Facebook、Flicker、Wikipedia 和其它大流量网站使用。Memcached 作为 Web 服务器和数据库之间的高速缓存层,可缩短服务器的响应时间。 FPGA 计算实例现在部署在数据中心,以加速以网络为导向的工作负载。

赛灵思 Virtex® UltraScale+™ FPGA 支持 -3、-2 和 -1 速度等级,其中 -3E 器件性能最高。-2LE 器件可以 0.85V 或 0.72V 的 VCCINT 电压工作,并提供更低的最大静态功耗。使用以 VCCINT = 0.85V 工作的 -2LE 器件时,L 器件的速度规格与 -2I 速度等级相同。

MAU 加速器可实现确定性的低尾时延和高吞吐量,无需在二者之间做权衡。这不仅有助于在给定的时延内使用更高质量的模型,而且还可显著节省基础架构成本并大幅降低能耗。 MAU 加速器运行在 Alveo U250 上,支持基于 ONNX 的行业标准开发流程

此参考设计是一款可配置电源解决方案,用于在各种用例中对整个 Xilinx® Zynq® UltraScale+ (ZU+) 系列MPSoC 器件进行处理。TPS65086x PMIC 拥有各种版本,因而此设计能够为从具有双核 Arm® Cortex®-A53应用处理器和双核 Arm Cortex-R5 实时处理器的基本ZU2CG 器件到更高端的 ZU7EV、ZU19EG 和ZU21DR 器件供电

在基于供电网络 (PDN) 的共振峰创建的布局前、布局后和系统验证数据模式中分析电源完整性对 FPGA DDR4存储器接口中的信号完整性的影响。使用 FPGA 配置的矢量网络分析仪 (VNA) 测量 PDN 阻抗曲线。创建多个测试数据模式,以便将电源的电流频谱分量与 PDN 共振峰叠加在一起,并演练传输线多次反射累积效应

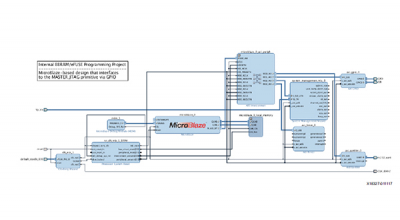

本文提供一个示例,演示如何在UltraScale™和UltraScale +™FPGA中对BBRAM和eFUSE进行内部编程。