Vivado Design Suite 用户指南:采用 IP 进行设计 (中文版) (v2020.1)

judy 在 周五, 10/09/2020 - 09:37 提交

本文描述如何使用 Vivado工具将来自赛灵思 IP 目录的即插即用 IP 模块(包括自定义封装的 IP)添加到您的设计中,并描述如何在设计中使用 IP、创建所需输出文件、管理和升级 IP 以及利用 IP 对设计进行仿真。

为智能硬件开发者、创客提供有关英特尔嵌入式处理器的相关文档、软件包、开源文档资料

本文描述如何使用 Vivado工具将来自赛灵思 IP 目录的即插即用 IP 模块(包括自定义封装的 IP)添加到您的设计中,并描述如何在设计中使用 IP、创建所需输出文件、管理和升级 IP 以及利用 IP 对设计进行仿真。

AuperaEdge AI 解决方案 - AUPV205 智能盒为视频流协议处理、解码、AI 分析和编码提供了完整的视频处理和 AI 分析管道解决方案。

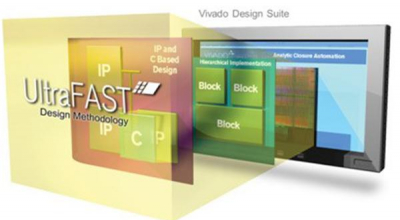

赛灵思可编程器件含有数百万个逻辑单元 (LC),并且集成的现代复杂电子系统也与日俱增。本高效设计方法指南提供了一整套最佳做法,旨在于较短的设计周期内完成此类复杂系统的创建。

基于 OVS 软件的解决方案不仅是 CPU 密集型的,这会影响系统性能,而且还会阻碍对可用带宽的充分利用。 用户将全部数据包处理功能卸载到 Xilinx Alveo 平台,不仅可节省 CPU 内核,而且还可提高数据包处理性能

本文描述了一种使用专用高速收发器的多速率串行接口。该设计基于非整数数据恢复单元,将数据速率下限扩展到0 Mb/s。

PowerAI Vision 使具有深度学习的计算机视觉更易为企业用户所用。现在,您可在 Xilinx® Alveo™ FPGA 上部署 POwerAI Vision 模型,并了解如何将 Vitis™ 库集成至面向 Vision AI 任务的整个工作流程中。

Messaging Classification Appliance(消息分类工具)由 Xilinx 和 Supermicro 合作推出,是一种预封装的软件和硬件解决方案,可通过理解语义内容(消息的含义和意图)实时大规模地过滤、分类和路由消息流。

移动互联网时代,每时每刻都在产生大量的图像和视频内容,内容提供商面临的主要问题是如何实现对内容的有效过滤,避免不允许的内容被公开。睿视演示了一种基于AI+FPGA的图像过滤方法,使用Xilinx Alveo加速器卡对特定图片/视频内容进行有效实时过滤。

本应用说明提供了一个包含控制逻辑的模块,用于将SMPTE UHD-SDI与UltraScale™ GTH收发器耦合,形成一个完整的UHD-SDI接口。本应用说明还提供了一个在Xilinx UltraScale FPGA KCU105评估板上运行的SDI设计示例。

Gemalto 的生物识别技术与基于 FPGA 的匹配引擎相结合,具有速度、成本降低、高能效、 可扩展性和灵活性方面的独特优势。