【下载】AXI 1G/2.5G 以太网子系统产品指南 (v7.2)

judy 在 周四, 01/28/2021 - 16:36 提交

实现三模(10/100/1000 Mb/s)以太网MAC或10/100 Mb/s以太网MAC。该核心支持使用MII、GMII、SGMII、RGMII和1000BASE-X接口将MAC连接到PHY芯片。它还为SGMII和1000BASE-X模式提供片上PHY。

为智能硬件开发者、创客提供有关英特尔嵌入式处理器的相关文档、软件包、开源文档资料

实现三模(10/100/1000 Mb/s)以太网MAC或10/100 Mb/s以太网MAC。该核心支持使用MII、GMII、SGMII、RGMII和1000BASE-X接口将MAC连接到PHY芯片。它还为SGMII和1000BASE-X模式提供片上PHY。

本文描述了在 Vivado® Design Suite 中创建、打包和重用自定义 IP 的过程。详细介绍了如何使用创建和包装 IP 向导来包装自定义 IP,包括 IP 集成器中开发的 IP 和高级 IP 包装选项。

本指南描述了配置为 PCI Express® 功能模式的 CPM 模块。

本文描述了如何使用Quad SPI和SD模式安全地启动Zynq®-7000 SoC,包括最佳使用RSA认证和AES加密。

快速傅立叶变换(FFT)已被广泛应用于各种信号处理算法中,这些算法通常需要可配置FFT大小的高吞吐量。本应用说明展示了在Xilinx® Versal™ AI Core器件中的AI Engine (AIE)阵列上高效的FFT实现。

多输入多输出(MIMO)技术已被许多无线系统采用,以利用信道的空间多样性。本应用说明展示了在Xilinx® Versal™ AI Core器件的AI Engine阵列上高效实现波束成形功能。

本文详细描述了 VCK190 评估板的功能。使用本指南开发和评估VCK190板上针对Versal ACAP XCVC1902器件的设计。

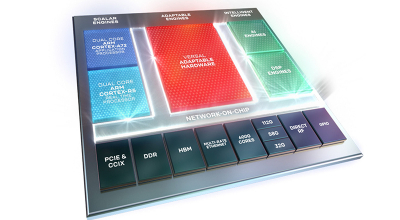

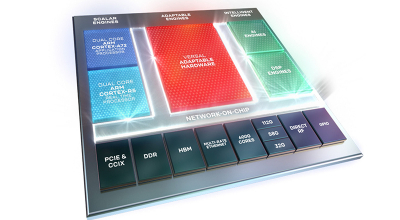

本文档旨在提供 Versal™ ACAP 硬件功能以及创建或移植设计时的块级注意事项的概述,并提供有关设计创建、仿真与调试的方法建议以及有关设计流程、启动和配置的建议。

在基于供电网络 (PDN) 的共振峰创建的布局前、布局后和系统验证数据模式中分析电源完整性对 FPGA DDR4 存储器接口中的信号完整性的影响。使用 FPGA 配置的矢量网络分析仪 (VNA) 测量 PDN 阻抗曲线。创建多个测试数据模式,以便将电源的电流频谱分量与 PDN 共振峰叠加在一起,并演练传输线多次反射累积效应

本文描述了用于 Zynq® UltraScale+™ MPSoC 的 Xilinx® LogiCORE™ IP H.264/H.265 视频编解码单元 (VCU) 内核。以60帧/秒的速度压缩/解压分辨率高达3840×2160 px的同步视频流。