【下载】使用 UltraScale和UltraScale+FPGA开发防篡改设计

judy 在 周三, 03/31/2021 - 16:24 提交

本应用笔记提供了防篡改(AT)指南和实际案例,以帮助保护UltraScale™和UltraScale+™ FPGA启用的系统中可能存在的IP和敏感数据。

为智能硬件开发者、创客提供有关英特尔嵌入式处理器的相关文档、软件包、开源文档资料

本应用笔记提供了防篡改(AT)指南和实际案例,以帮助保护UltraScale™和UltraScale+™ FPGA启用的系统中可能存在的IP和敏感数据。

Xilinx自适应器件的灵活性和可配置性与IP和工具产品相结合,可显著提高安全处理性能。

赛灵思 Versal ACAP 硬件、IP 和平台开发方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。Versal ACAP从设计之初即采用正确方法并尽早关注设计目标(包括 IP 选择和配置、块连接、RTL、时钟、I/O 接口和 PCB 管脚分配)至关重要。

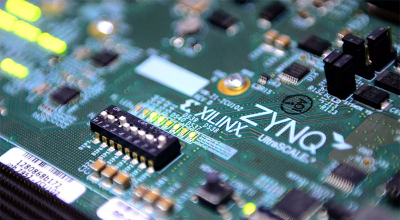

Xilinx公司采用InFO封装的新型Zynq UltraScale+ MPSoC实现了全方位的工业性能--所有这些器件都采用了具有高计算密度的紧凑外形。

本文档旨在描述推荐的设计方法,帮助用户在 Vivado® Design Suite 中有效利用赛灵思 FPGA 器件资源,并加速完成设计实现和时序收敛。提供推荐方法背后的原理,以支持用户制定出明智的设计决策。

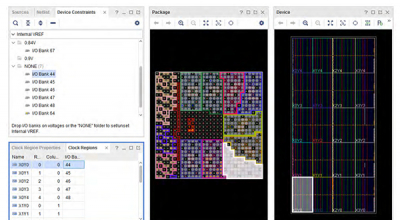

本文描述了I/O规划过程,在RTL设计中与PCB设计人员一起执行端口分配,并与系统工程师一起利用目标Xilinx FPGA上的时钟资源;使用Vivado设计套件减少内部和外部导线长度,提高系统性能。

本文描述了Xilinx®Alveo™SN1000 SmartNIC的规范。

本文提供Versal™ ACAP编程和设计的软件专用信息。

低密度奇偶校验(LDPC)软IP内核支持LDPC解码和编码。所使用的LDPC码是高度可配置的,并且所使用的特定代码可以在逐个码字的基础上指定。

该应用说明为基于AXI的嵌入式设计提供了PL和PS安全和隔离的桥梁。