用于 AI 推理的 VCK5000 产品简介

judy 在 周五, 08/13/2021 - 09:34 提交

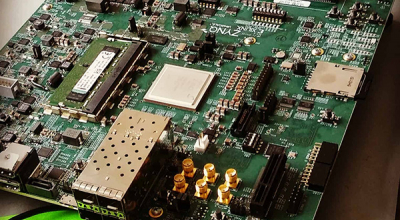

Xilinx VCK5000 Versal 开发卡基于Xilinx 7nm VersalACAP架构构建,专为高吞吐量AI推理和高性能计算应用而设计。VCK5000具有标准化的软件开发流程,可提供比当今服务器级CPU高100倍的计算能力,并且比当今服务器级GPU更好的MLPerf推理性能,是云加速和边缘计算应用的理想开发平台。

为智能硬件开发者、创客提供有关英特尔嵌入式处理器的相关文档、软件包、开源文档资料

Xilinx VCK5000 Versal 开发卡基于Xilinx 7nm VersalACAP架构构建,专为高吞吐量AI推理和高性能计算应用而设计。VCK5000具有标准化的软件开发流程,可提供比当今服务器级CPU高100倍的计算能力,并且比当今服务器级GPU更好的MLPerf推理性能,是云加速和边缘计算应用的理想开发平台。

靠近模拟-数字边界边缘节点的位置对真实环境的即时响应受高度重视,众多市场领域存在迫切需求。Versal™ ACAP 产品组合 AI Edge 系列则应运而生,作为一种领域专用架构 (DSA),有效满足 7nm 芯片工艺系统提出的严苛要求。

本文描述如何使用 Dynamic Function eXchange 灵活高效地使用硬件资源来动态更新已部署的系统。包括对技术历史的回顾。

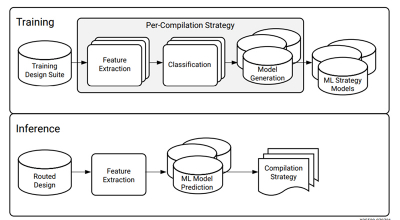

本白皮书描述智能设计如何使用机器学习和基于规则的系统来模拟时序收敛专家并提高生产力。

为处理海量数据、复杂算法、超低延时的应用提供数字化加速驱动力是赛灵思一直的目标。为此,赛灵思研发 Bootgen 工具支持将二进制文件缝合在一起并生成器件启动镜像定义了多个属性和参数作为创建启动镜像时的输入。

SmartLynq+ 模块的构建旨在满足高速调试和跟踪需求,主要面向使用Versal™ 平台的开发者。与此前的赛灵思调试产品相比,SmartLynq+ 模块通过 HSDP 可将 Linux下载时间加快高达28倍,将数据捕获速度提高100倍。更快的迭代和重复下载既提高了开发效率,也缩短了设计周期。

本文描述了如何使用 XMPU、XPPU 和 TrustZone 提供的硬件和软件机制进行子系统的隔离。

描述使用 Vivado® Design Suite 生成加密比特流和加密密钥的分步过程。

本文将重点介绍 PolarFire FPGA 和 Teledyne e2v DDR4T04G72 之间点对点的连接的例子,以及多个 DDR4器件如何与一片 Xilinx KU060 FPGA 连接。

实现确定性延迟是当今许多系统设计中讨论的主题。过去,人们一直在努力提高数据传输速度和带宽。如今的应用则越来越重视确定性——即要求数据包在精确的、可重复的时间点传送。本文将在设备的层面讨论确定性这一主题,以及如何设计超高速数据转换和信号处理系统以保证确定性延迟。