【视频】使用 Vitis 加速库进行开发

judy 在 周二, 10/26/2021 - 09:50 提交

通过本次研讨会,了解所提供的不同层次的抽象,查看通过使用 Vitis 库启动设计的演示预演并了解您可实现的性能优势。

Vitis 是由赛灵思(Xilinx)推出的一款开发工具套件,用于加速应用程序的开发和部署,尤其专注于基于赛灵思的可编程逻辑设备(FPGA)的加速。

Vitis 工具套件的目标是简化 FPGA 加速应用程序的开发流程,使更广泛的开发者能够充分利用 FPGA 提供的硬件加速性能,从而加速特定领域的计算任务。

通过本次研讨会,了解所提供的不同层次的抽象,查看通过使用 Vitis 库启动设计的演示预演并了解您可实现的性能优势。

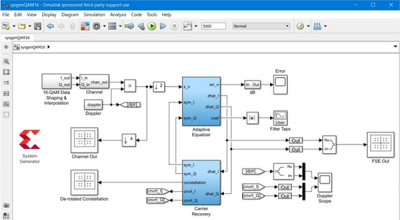

本文描述如何执行基于模型的设计,在 Simulink 环境中实现快速设计探索,并通过自动代码生成加速 Xilinx 器件的生产路径。

学习如何在 ZCU104 评估板上使用 VCU、DPU 和 PL 来构建和运行视频分析示例应用。

为期2天的培训课程,介绍了基于Vitis HLS工具的综合策略、特性,如何最优化吞吐量、面积、延迟、接口创建、仿真代码编辑和编码注意事项;最终,还将通过基于图像处理的实际案例分享,给学员展示完整的Vitis HLS工程开发过程,以及如何进行有效的设计优化和调试。

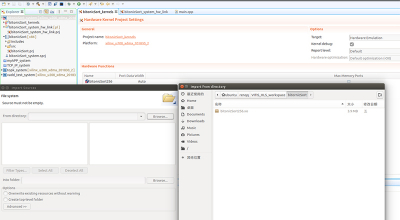

本视频展示了如何使用智能模型选型示例开始使用 VVAS。

VVAS 是一个完整的软件堆栈,用于在所有 Xilinx 平台上构建基于 AI 的智能视频分析解决方案!在短短几周内实现从概念到实时部署。

Xilinx 多任务模型旨在同时完成不同的图像感知任务,同时实现高性能和高效率。凭借 MTLv3 模型,以及在 Vitis AI 的助力下,现可实现面向车辆检测、车道检测、分割、可行驶区域检测和深度评估的 5 个任务,基于一个模型,在边缘实时速度运行。

HLS导出的.xo文件如何导入到Vitis里面?需要把.xo文件解压,然后把文件夹导入到Vitis Kernel/src文件夹下吗?

为了使广大开发者学新学透,赛灵思开发者社区与电巢直播间特别邀请到两位赛灵思专家为大家分享Vitis及Vitis AI是如何在赛灵思异构平台(包括FPGA, SoC, Versal ACAP) 上实现嵌入式软件和加速应用。欢迎您点击关注,届时收看。

赛灵思 Vitis AI 是一款功能强大的机器学习开发平台,用于在赛灵思自适应计算平台上实现 AI 推断加速。最新发布的 Vitis AI 1.4 版本为用户提供了完整的解决方案堆栈,首次实现了对最新 7nm Versal ACAP 平台和16nm Kria™ SOM的支持。