米联客浅谈Xilinx FPGA BRAM的基本使用

judy 在 周一, 06/06/2022 - 17:03 提交

Xilinx系列FPGA,包含两种RAM:Block RAM和分布式RAM(Distributed RAM),他们的区别在于,Block RAM是内嵌专用的RAM,而Distributed RAM需要消耗珍贵的逻辑资源组成。

Xilinx系列FPGA,包含两种RAM:Block RAM和分布式RAM(Distributed RAM),他们的区别在于,Block RAM是内嵌专用的RAM,而Distributed RAM需要消耗珍贵的逻辑资源组成。

本文介绍了当MicroBlaze包含在DFX可重构模块(RM)内时,更新MicroBlaze Block RAM的内容。

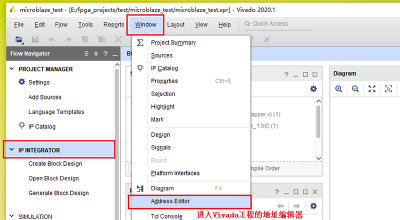

修改了代码后编译工程,有时会因为BRAM空间不足而编译失败,出现下面的错误提示,这时,需要回到Vivado工程里面,在Block Design中将分配的BRAM空间大小改大。具体方法如下。

有时CPU需要与PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现此要求。本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。

XILINX 系列的 FPGA ,如果想要做一个 RAM,有两种方式:

1、使用逻辑资源组成分布式 RAM,即 Distributed RAM

2、使用 XILINX 专用的 Block RAM,即 BRAM

无论是7系列FPGA、UltraScale还是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我们所说的URAM。BRAM和URAM都是重要的片上存储资源,但两者还是有些显著的区别。

Block RAM与Distributed RAM,简称为BRAM与DRAM, 要搞清楚两者的区别首先要了解FPGA的结构: FPGA=CLB + IOB+Block RAM CLB。一个CLB中包含2个Slice、8位寄存器、多路选择器、进位链等。

背景:我们需要仿照ZynqNet的模式构造卷积的IPcore用于FPGA的优化。

目的:搞懂zynqNet的cache的实现。

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将结果打印输出到串口终端显示。

涉及到AXI BRAM Controller 和 Block Memery Generator等IP的使用。