在Vivado 2020.1中用MIG核读写DDR3内存,编译代码时提示Sub-optimal placement错误的解决办法

judy 在 周五, 10/15/2021 - 10:16 提交

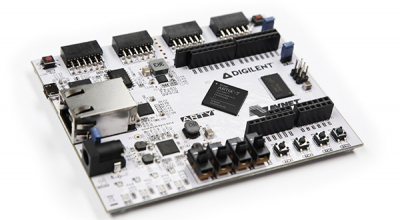

板子使用的是米联客的XC7A35TFGG484-2的开发板,上面带有256MB的型号为Micron MT41K128M16的DDR3内存。板子上的V4引脚上接了50MHz的晶振。

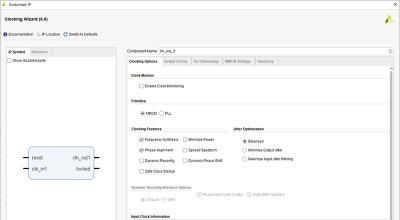

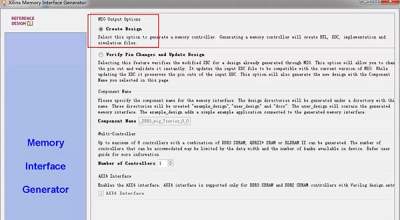

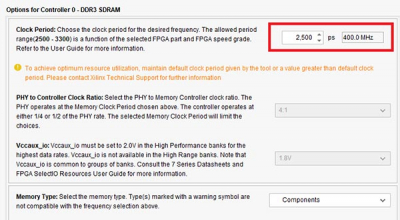

用MIG核来驱动这片DDR3内存。DDR3的运行时钟Clock Period为400MHz(由MIG核自己产生这个时钟,从ddr3_ck_p和ddr3_ck_n引脚输出出来,用来驱动DDR3)