快速上手Xilinx DDR3 IP核(3)——把MIG IP核封装成一个FIFO(上)(Native接口)

judy 在 周三, 03/02/2022 - 11:29 提交

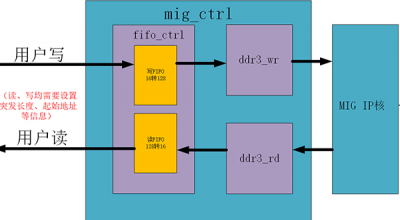

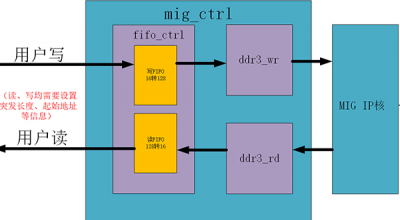

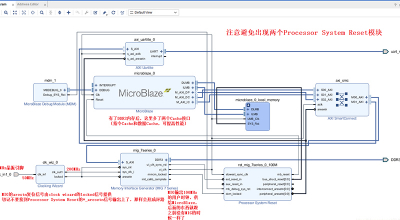

本文将把Xilinx的MIG IP核DDR3的Native接口进行二次封装,将其封装成一个类似FIFO的接口,使其应用起来更加方便简单。

本文将把Xilinx的MIG IP核DDR3的Native接口进行二次封装,将其封装成一个类似FIFO的接口,使其应用起来更加方便简单。

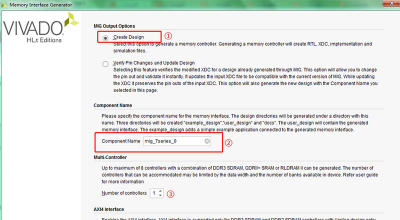

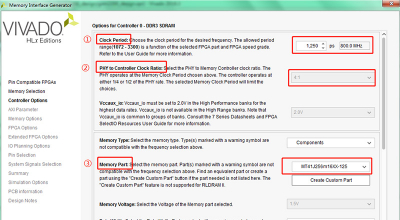

在我心中,Xilinx是一家完美的公司,技术生态支持实在是做的太好了。Xilinx也知道我们不会用DDR3,所以提供了一个example design给你学习,怎么样?惊不惊喜?意不意外?

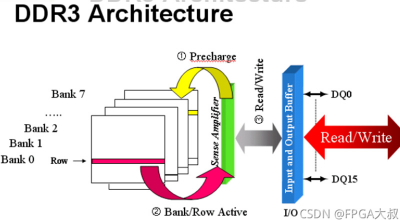

DDR3 SDRAM 简称 DDR3,是当今较为常见的一种储存器,在计算机及嵌入式产品中得到广泛应用, 特别是应用在涉及到大量数据交互的场合

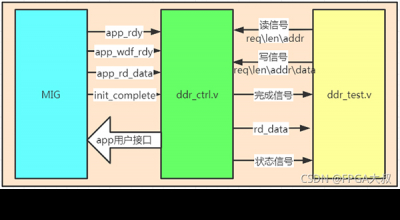

为了更方便的对DDR读写,我们对DDR再次封装成可复用的读写模块。

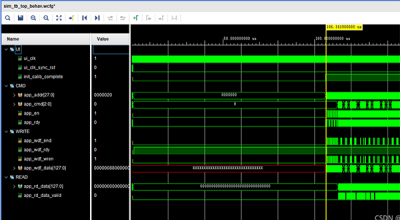

了解ddr的仿真模型建立

实验任务:将输入数据(data_in)存入ddr,然后读出,验证输入输出数据是否相等。

干货来了,用DDR搬砖,只需要会用IP就好,Xilinx官方YYDS!

对FPGA而言,时钟就是脉搏,必须理解透彻!

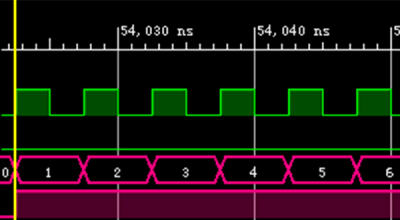

DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据的读取写入是按时钟同步的

添加了DDR3内存以后,程序既可以运行在BRAM里面,也可以运行在DDR3内存里面。但如果运行在DDR3内存里面,固化起来会比较麻烦,需要借助SREC SPI Bootloader。