Xilinx FPGA DDR3设计(三)DDR3 IP核详解及读写测试

judy 在 周二, 06/06/2023 - 15:33 提交

本文我们介绍下Xilinx DDR3 IP核的重要架构、IP核信号管脚定义、读写操作时序

本文我们介绍下Xilinx DDR3 IP核的重要架构、IP核信号管脚定义、读写操作时序

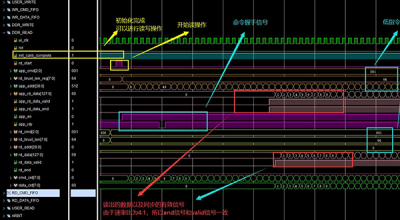

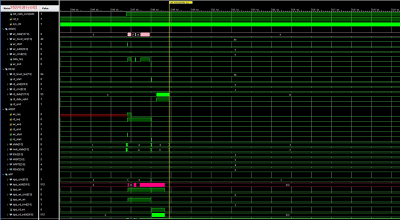

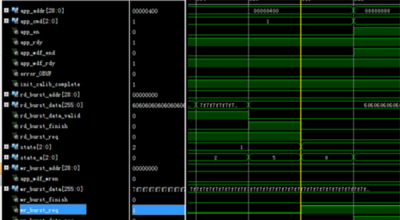

在之前设计的 DDR3 控制器的基础上,添加用户写、读模块,便于在用户端更容易的对 DDR3 进行写读控制

在读写模块的基础上添加 FIFO 接口,包括写指令 FIFO、写数据 FIFO

在实验的基础上添加一个仲裁模块,控制写读指令的执行。

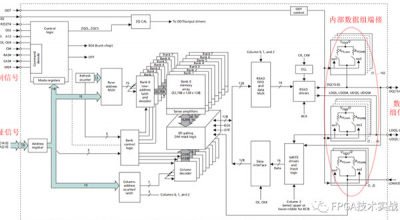

MIG IP控制器是Xilinx为用户提供的一个用于DDR控制的IP核,方便用户在即使不了解DDR的控制

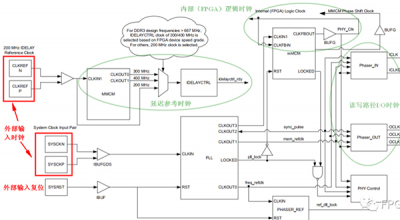

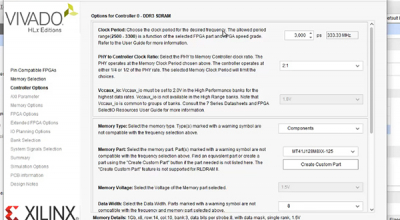

本文介绍Xilinx FPGA外接DDR3时钟相关参数及配置。

本文介绍DDR3控制器(MIG)各个时钟的含义

本文我们介绍下DDR3的基础知识,涉及DDR3管脚信号、容量计算、重要参数介绍内容

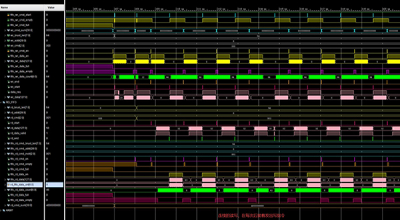

DDR接口信号分为DDR对外接口信号、用户应用接口信号和读写控制信号。对外接口信号直接与DDR芯片连接,用户应用接口信号为DDR控制器IP输出信号

本文将把Xilinx的MIG IP核DDR3的Native接口进行二次封装,将其封装成一个类似FIFO的接口,使其应用起来更加方便简单。