DDR3和mig的介绍

judy 在 周五, 02/22/2019 - 15:26 提交

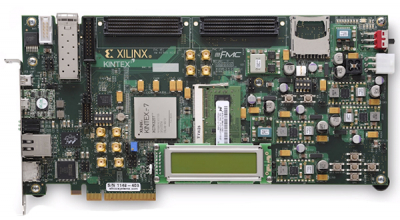

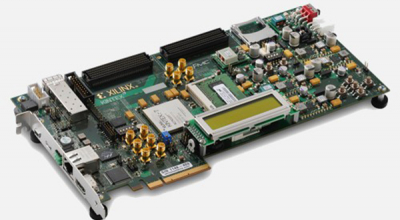

FPGA开源工作室将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

FPGA开源工作室将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

视频演示了 DDR3 内存的 Kintex-7 FPGA 接口功能。

作者:OpenSLee ,来源:FPGA开源工作室

1. 背景

这篇文章主要介绍了DDR3IP核的写实现。

DDR3:使用流程

一. 配置过程

1>首先找到IP核

作者:张凤麒,张延彬,王忠勇;2018年电子技术应用第7期