基于FPGA+GPU异构平台的遥感图像切片解决方案

judy 在 周一, 04/07/2025 - 09:30 提交

中科亿海微自主研制的AI目标识别加速卡,基于FPGA+GPU异构并行计算处理架构设计,内嵌深度学习AI推理框架引擎,可实现图像处理的目标识别加速应用。

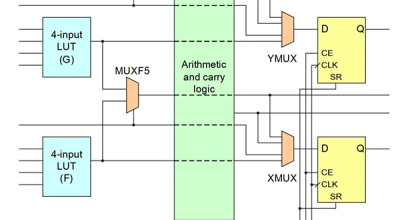

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

中科亿海微自主研制的AI目标识别加速卡,基于FPGA+GPU异构并行计算处理架构设计,内嵌深度学习AI推理框架引擎,可实现图像处理的目标识别加速应用。

如今,边缘采集的数据量十分庞大。据 Gartner 预测,到 2025 年,将有多达 75% 的企业数据会在传统数据中心以外生成

本例程采用基于SPI Master和BPI Master接口的远程升级方案,在远程升级的过程中,用户通过通信协议或专用接口从远端接收位流

本文将详细分析这些步骤中的优化挑战,并提出一些可能的解决方案,以帮助设计者在保证仿真性能的同时,最大限度地减少编译时间。

今天主要对Xilinx、Altera和Actel三家 FPGA 中使用的逻辑单元架构进行对比,最后对这三家逻辑量换算进行说明

本文介绍的中科亿海微基于FPGA+SoC架构的通用AI图像推理模组,主要应用于图像处理领域,用于图像采集、图像处理和目标识别。

PolarFire SoC FPGA已通过汽车行业1级温度认证,支持-40°C至125°C工作范围。

亿海神针EQ6HL130P可编程逻辑芯片具备240个高速18x18位乘法器,具有8个可编程PLL,最高时钟管理频率可达500MHZ

近年来,国产 FPGA 发展迅速,中国共有22家(去除特殊用途的反熔丝还有19家)FPGA厂商,主要有紫光同创、安路科技、复旦微等。

本文将为大家详细介绍在 Linux 系统中通过预留物理内存实现 ARM 与 FPGA 高效通信的方法