PYNQ框架下用Python编程FPGA不是梦-Vitis HLS前端开源

judy 在 周一, 03/15/2021 - 16:18 提交

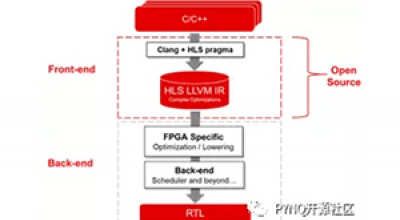

目前,虽然基于C/C++等高层次综合相较于手写RTL层级HDL语言已大幅提升了开发效率,但随着相关技术的不断进步,以及算法迭代的日益频繁,人们似乎并不满足于此。

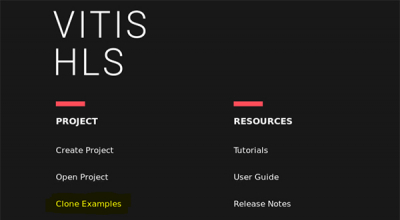

不少刚刚接触到Pynq的用户第一个问号?Pynq是不是用Python编程FPGA的新物种?

目前,虽然基于C/C++等高层次综合相较于手写RTL层级HDL语言已大幅提升了开发效率,但随着相关技术的不断进步,以及算法迭代的日益频繁,人们似乎并不满足于此。

不少刚刚接触到Pynq的用户第一个问号?Pynq是不是用Python编程FPGA的新物种?

在论坛上遇到在高层次综合工具中调用视觉库遇到的大多数问题都和 opencv 库以及Xilinx Vision 库的安装路径有关,如今 Vitis HLS 2020.1 之后的版本都不再提供OpenCV 的预编译库,就更需要开发者们将各自工作环境中的库路径,环境变量都设置好。希望这篇博文能给大家调用 Vitis Vision Library 提供向导,提升效率。

您是否想创建自己带有 AXI4-Lite 接口的 IP 却感觉无从着手?本文将为您讲解有关如何在 Vitis HLS 中使用 C 语言代码创建 AXI4-Lite 接口的基础知识。