Vitis_ZCU102_1_Hello Vitis

judy 在 周四, 03/19/2020 - 10:33 提交

作者:bt_

原文链接: https://blog.csdn.net/botao_li/article/details/103901856

* 本文由作者授权转发,如需转载请联系作者本人

主要参考:ug1400

安装串口调试软件

安装串口软件 tinyserial

本人使用 Qt 5.12.6 编译后使用(deb 安装后无法运行)。

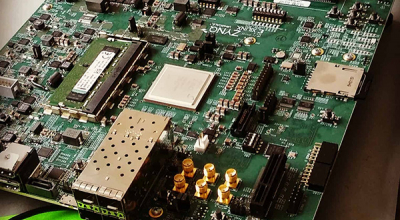

建立 Platform Project