24 个让 Python 加速的好方法

judy 在 周五, 07/19/2019 - 09:22 提交

24 个让 Python 加速的好方法

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

24 个让 Python 加速的好方法

图像处理简而言之就是对图像进行操作从而得到自己想要的结果,它是一个非常广义的概念,包含图像增强、图像复原、图像重建、图像分析、模式识别、计算机视觉等N多个应用方向。这些应用技术有许多在本质上是相通的,但是不同应用领域的关注点往往是不同的

前几天聊天聊到在Linux系统下调用SDK的gnu交叉编译工具链的问题,Panda同学是这么做的,简单写几句分享一下。按照正常套路,我们会专门下载第三方交叉编译工具链进行Xilinx器件的Linux开发

Verilog语言和VHDL语言是两种不同的硬件描述语言,但并非所有人都同时精通两种语言,所以在某些时候,需要把Verilog代码转换为VHDL代码。本文以通用的XHDL工具为例对Verilog转换到VHDL过程中存在的问题进行了总结

本篇完成对HDMI显示代码的UVM仿真,梳理一下在windows-modelsim工具下UVM仿真环境的建立,调试以及遇到的问题。仿真的架构在上一篇已经做了简要介绍,这部分做重点讲解

文章阐述了Xilinx FPGA可编程的本质,逆向分析破解了FPGA编程的bit流文件,并将其与FPGA内部电路相对应,对于深度理解动态可编程及FPGA电路结构具有重要的指导价值,LUT动态可编程使得FPGA内部的资源使用起来更灵活,你可以把LUT当成BRAM使用,也可以随时改变若干个LUT组成电路完成的硬件功能

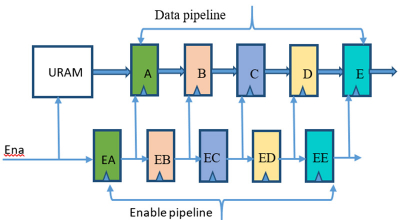

UltraRAM 原语(也称为 URAM)可在 Xilinx UltraScale +™ 架构中使用,而且可用来高效地实现大容量深存储器。URAM 原语具有实现高速内存访问所需的可配置流水线属性和专用级联连接。 流水线阶段和级联连接是使用原语上的属性来配置的。 本篇博文描述的是通过将 URAM 矩阵配置为使用流水线寄存器来实现最佳时序性能的方法。

无线设备和其处理的数据量每年都呈指数递增(53% 复合年增长率。随着这些设备产生并处理的数据量越来越多,连接这些设备的无线通信基础设施也必须持续发展才能满足需求。如图 1 所示,4G 网络频谱效率的提高已经不足以提供 3GPP[2] 定义的三大高级 5G 用例所需数据速率的阶梯函数了

Verilog HDL (Hardware Description Language) 是一种硬件描述语言,可以在算法级、门级到开关级的多种抽象设计层次上对数字系统建模。它可以描述设计的行为特性、数据流特性、结构组成以及包含响应监控和设计验证方面的时延和波形产生机制

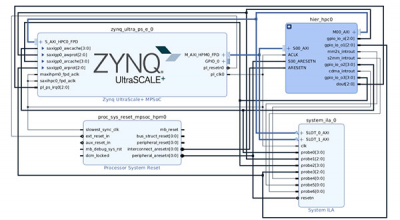

为了使相关传输被CCI监听,需要设置寄存器lpd_apu的最低两位为1,而且必须在A53处于复位态时设置。我们利用MPSoC BootROM在加载时设置寄存器lpd_apu。

为了用MPSoC BootROM在加载时设置寄存器lpd_apu,需要准备寄存器初始化文件,并且使用寄存器初始化文件创建启动文件boot.bin