硬件仿真世界

judy 在 周一, 04/01/2019 - 15:57 提交

如果您是贸然进入了高速设计领域的新手工程师之一,并且被“信号完整性仿真”这个术语所震撼,请不要烦恼。 在这次博客之旅中,我们先来回顾一下基础知识,然后再介绍一些更高深的话题。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

如果您是贸然进入了高速设计领域的新手工程师之一,并且被“信号完整性仿真”这个术语所震撼,请不要烦恼。 在这次博客之旅中,我们先来回顾一下基础知识,然后再介绍一些更高深的话题。

数字电路设计中一般包括3个大的阶段:源代码输入、综合和实现,而电路仿真的切入点也基本与这些阶段相吻合,根据适用的设计阶段的不同仿真可以分为RTL行为级仿真、综合后门级功能仿真和时序仿真。这种仿真轮廓的模型不仅适合FPGA/CPLD设计,同样适合IC设计

SystemVerilog 接口的开发旨在让设计中层级之间的连接变得更加轻松容易。 您可以把这类接口看作是多个模块共有的引脚集合。与必须在每个模块上定义多个引脚不同的是,您只需在接口中对引脚定义一次,之后只需在模块上定义接口即可。 如果稍后接口中涉及的信号被更改,则仅需更改接口即可

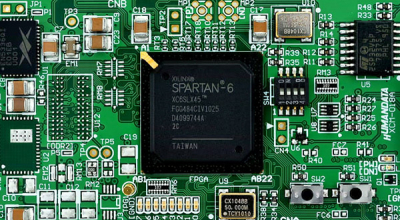

如果符合一些简单的设计原则,采用最新的Xilinx7系列FPGA架构上实现无线通信。Xilinx公司已经创建了典型无线数据路径的设计范例,表明中速级(-2)器件上使用的几乎100%的 slice资源都支持500 MHz以上的时钟频率。如何真正时序高速设计,需要注意一下几点

Alveo 数据中心加速卡在硬件中配置了两个 QSFP 端口。这些如何用于在 U200/U250 卡上启用以太网子系统 IP?

利用卷积神经网络(Convolutional Neural Network, CNN) 等深层神经网络的解决方案,可以逐渐取代基于算法说明的传统图像处理工作。尽管图像预处理、后期处理和信号处理仍采用现有方法进行,但在图像分类应用中(缺陷、对象以及特征分类),深度学习变得愈加重要

FPGA设计的特点是需要不断不断的迭代各个设计流程来达到最终的设计,同时迭代的成本大,它比单片机开发更注重迭代的开发思想。所以,设计的前期一定要从系统的角度考虑好系统的方案,然后在系统这个方案中不断的迭代,不然后期发现由于系统方案的问题就得不偿失了,好的系统架构就是成功一大半了

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 答案应该与上面问题一致。同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变

针对CMOS图像传感器采集图像过程中的噪声预处理问题,提出一种在FPGA中实现的可配置的自适应加权均值滤波模块设计方案。该模块通过检测滤波窗口内不同方向的方差来确定纹理方向,从而自动生成相应的加权系数,可以对宽度不超过4 094像素的图像进行流水线式的加权均值滤波处理,达到去噪保边的目的

Vivado是Xilinx公司的FPGA开发工具,熟悉Xilinx的工程师应该对ISE比较不陌生,但是随着时代的发展,FPGA芯片进步很快,Xilinx也已经宣布不再对ISE进行更新,这就意味着Vivado将在以后的发展中逐渐取代ISE,所以掌握好Vivavo的使用,是一个FPGA工程师必备的技能。今天的文章主要是讲解怎么调用Modelsim进行仿真