mig IP用户读写时序

judy 在 周四, 02/28/2019 - 09:32 提交

对于mig与DDR3/DDR2 SDRAM的读写时序我们不需要了解太多,交给mig就可以了。我们需要做的是控制好User Interface,写出正确的User logic。想要写好Userlogic,我们就必须清楚每一个用户控制接口的含义

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

对于mig与DDR3/DDR2 SDRAM的读写时序我们不需要了解太多,交给mig就可以了。我们需要做的是控制好User Interface,写出正确的User logic。想要写好Userlogic,我们就必须清楚每一个用户控制接口的含义

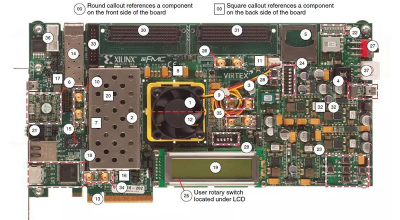

随着FPGA在数据中心加速和Smart NIC在SDN和NFV领域的广泛应用,基于以太网接口的FPGA开发板越来越受到关注。而更高速率的以太网接口技术则是应用的关键,本文将详细介绍基于FPGA的10G以太网接口的原理及调试技术。

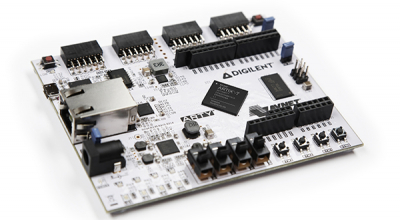

FPGA开源工作室将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。软件使用Vivado 2018.1

本文旨在让无线电工程师熟悉一种现成的多用途软件无线电(COTS SDR)平台,该平台可以缩短5G的开发时间。

FPGA开源工作室将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

Xilinx 7系列FPGA全系内置了一个ADC,称呼为XADC。这个XADC,内部是两个1mbps的ADC,可以采集模拟信号转为数字信号送给FPGA内部使用。XADC内部可以直接获取芯片结温和FPGA的若干供电电压(7系列不包括VCCO),用于监控FPGA内部状况

NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车场景中摄像头系统的快速启动时间要求就是很好的一个例子——车辆启动后后视图像在仪表板显示屏上的显示速度是最为突出的设计挑战

在远程更新的时候,有时候需要双镜像来保护设计的稳定性。在进行更新设计的时候,只更新一个镜像,另一个镜像在部署之前就测试过没问题并不再更新。当更新出错时,通过不被更新的镜像进行一些操作,可以将更新失败的数据重新写入Flash。这样即使更新出错,也能保证设计至少可以被远程恢复。本文对Xilinx 7系列的Multiboot做一些简单介绍。

初识Python语言,觉得python满足了我上学时候对编程语言的所有要求。python语言的高效编程技巧让我们这些大学曾经苦逼学了四年c或者c++的人,兴奋的不行不行的,终于解脱了。高级语言,如果做不到这样,还扯啥高级呢?

本文总结了深度学习中常用的八大类型的卷积,以非常形象的方式帮助你建立直觉理解,为你的深度学习提供有益的参考。