max_fanout命令的正确打开方式

judy 在 周二, 01/08/2019 - 09:32 提交

vivado自带很多命令帮助编译器更好的实现设计者的想法,用得好会变成开发利器。比如,max_fanout命令,本身是用来约束扇出,减少布线拥塞的常用命令。然而很多读者向我反映,使用这个命令之后发现没有任何事情发生,完全没有任何效果。这里我就带大家理一理这个命令的使用方法

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

vivado自带很多命令帮助编译器更好的实现设计者的想法,用得好会变成开发利器。比如,max_fanout命令,本身是用来约束扇出,减少布线拥塞的常用命令。然而很多读者向我反映,使用这个命令之后发现没有任何事情发生,完全没有任何效果。这里我就带大家理一理这个命令的使用方法

本篇主要介绍Xilinx FPGA PL侧的IO资源,目前主要包括HP、HR、HD三种类型,不同架构、不同封装的FPGA,包含的IO资源种类和数量均不一样,在连接外设时一定要注意,比如3.3V逻辑电平就不能直接连接到HP bank上,其VCCO的电源电压也不能直接接3.3V

电磁频谱是战争领域中争议越来越大的话题。 电子对抗措施日益复杂,探测第五代战斗机变得更加困难,大多数世界主要大国正大力投资到网络战技术,以便未来成为这一领域的主导者。 此外,随着蜂窝电话供应商开始推出5G,汽车制造商推动V2X通信,以及物联网将无线连接推向无数设备,频谱的商业用途呈指数级扩展。

本篇主要介绍UFS的架构、系统模型、信号定义(包括eUFS和UFS Card)等,以对UFS接口有个粗略的了解。下一篇将针对电源、复位、时钟等部分进行详细介绍。

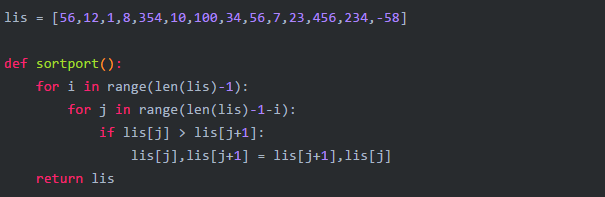

1、冒泡排序

2、计算x的n次方的方法

本文主要介绍Zynq UltraScale + MPSoC系列芯片的USB3.0/2.0接口硬件设计。

无线工程师经常希望使用无线信号实现从概念到原型。诸如USRP(通用软件无线电外设)设备的软件无线电(SDR)提供了满足该需求的灵活解决方案

在2010年4月硅谷举行的嵌入式系统大会上,赛灵思发布了可扩展处理平台的架构详情,这款基于无处不在的ARM处理器的SoC可满足复杂嵌入式系统的高性能、低功耗和多核处理能力要求

如何存储关键数据的方法,属于规模测试验证的手段,但对于Verilog的调试过程还不够直观,因为无法确切地了解Verilog代码仿真中各个关联信号是如何作用的。Verilog的确可以像C/C++一样启动调试模式,针对每行代码进行调试。但请注意,由于Verilog是并行执行的,而仿真是采用delta时间逐步并行推进的,采用代码调试较为困难,所以常常需要存储全部或部分仿真数据,这就是波形文件。

本篇主要介绍PCIe总线的AC耦合电容、总线的去加重等高速信号调整技术。