Vivado 2018.2.x 及更早版本的设计咨询——生成的、引用错误主时钟的时钟会导致不正确的时钟偏移

judy 在 周四, 12/27/2018 - 14:32 提交

本设计咨询主要介绍一个错误的时钟偏移计算导致错误时序收敛的问题。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

本设计咨询主要介绍一个错误的时钟偏移计算导致错误时序收敛的问题。

本文为在FPGA中支持DSR协议的路由表项管理功能,设计一种基于有限状态机[8]的实现方法。本文的设计中,状态机包含一个初始状态和3个功能状态。有限状态机的3个功能状态一起联合实现路由存储、路由查找、路由删除的功能。有限状态机使得硬件代码符合时序电路的风格

篇主要介绍PCIe总线的复位方式。

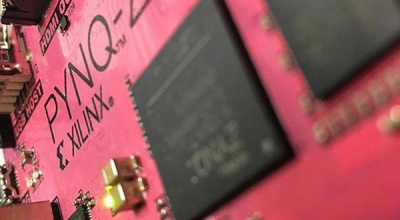

Zynq在PS和PL之间有9个AXI接口。 在PL方面,有4x AXI Master HP(高性能)端口,2x AXI GP(通用)端口,2x AXI Slave GP端口和1x AXI Master ACP端口。 PS中还有连接到PL的GPIO控制器

本片主要介绍PCIe总线的电源管理,主要包括不同板卡的功耗、板卡的能耗等级等。

多年来,数字收发机被应用在多种类型的应用中,包括地面蜂窝网络、卫星通信和基于雷达的监视、地球观测和监控。它们的性能直接影响新的5G移动网络的效率和系统成本。在讨论最新一代的高速数据转换器如何实现这些优势之前,让我们先看一看两种不同的收发机系统的架构。

本篇主要介绍PCIe总线相关的信号

用HDL语言+Vivado创建一个挂载在AXI总线上的自定义IP核

本篇主要针对Zynq UltraScale + MPSoC的DDR接口,从硬件设计的角度进行详细介绍,最后展示一下小编之前自己设计的基于ZU+的外挂8颗DDR4的设计

本教程旨在指导用户通过 Plunify Cloud 的云服务器,来使用 InTime 软件优化 FPGA 设计