7 种简洁 Python 语法,教你码出一手好代码

judy 在 周三, 01/16/2019 - 09:41 提交

Python 是一门用途广泛、易读、而且容易入门的编程语言。但同时 python 语法也允许我们做一些很奇怪的事情。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

Python 是一门用途广泛、易读、而且容易入门的编程语言。但同时 python 语法也允许我们做一些很奇怪的事情。

神经网络(NN)几乎可以在每个领域帮助我们用创造性的方式解决问题。本文将介绍神经网络的相关知识。读后你将对神经网络有个大概了解,它是如何工作的?如何创建神经网络?

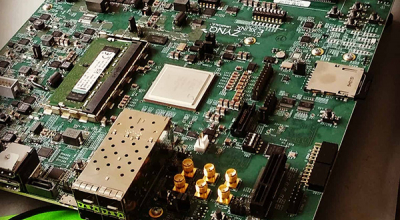

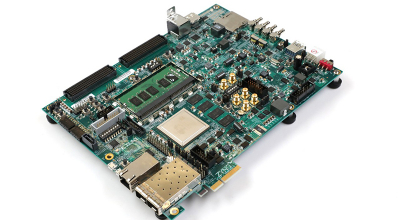

本篇主要介绍Xilinx FPGA的电源设计,主要包括电源种类、电压要求、功耗需求,上下电时序要求,常见的电源实现方案等。

Python是一门简单易学的编程语言,语法简洁而清晰,并且拥有丰富和强大的类库。与其它大多数程序设计语言使用大括号不一样 ,它使用缩进来定义语句块。在平时的工作中,Python开发者很容易犯一些小错误,这些错误都很容易避免,本文总结了Python开发者最容易犯的10个错误,一起来看下,不知你中枪了没有。

当我和人们谈起FPGA时,我听到很多人说:“我不知道它们的工作原理”、“它们太复杂了”、“我无法用C语言编程”。我不希望看到这样一种神奇的器件遭受如此冷遇,因此下面我将尝试解答一些常见问题

该系列文章介绍MIPI系列规范。本篇为第一篇,主要介绍MIPI Alliance及其推出的一系列规范,以及相关的一些应用,以便对MIPI有一个全面的了解。后续会针对每一个部分进行详细介绍。

1、MIPI Overview

DDS直接数字式频率合成器(Direct Digital Synthesizer)。本文实现一个具有可以频率可调、相位可调的正余弦、方波、三角波的DDS。

内核重置应该保持断言状态,直到相关时钟稳定为止。在从重置中取出以太网 IP 核之前,它必须具有稳定的频率而且没有故障。 这适用于 SerDes 时钟和 IP 核时钟。 如果在一个时钟中检测到后续不稳定性,就必须重置 100G 以太网 IP 核。

很多使用ZCU106/104开发板的小伙伴,发现在官网上可以找到包括IPI,MIG,PCIe等参考设计,但是如何把VCU用起来的流程设计,Target Reference Design(以下简称TRD)不知道哪里去下,那么最新版本的TRD去哪里获得呢?

为了复用现有的MATLAB®代码,LabVIEW Communications System Design Suite (LabVIEW Comms) 新增了MATLAB专用接口的功能。无线原型的开发者可使用已有的MATLAB函数或脚本,将其连接至LabVIEW Comms在Windows处理器上运行的代码部分